# **EPSON**

EPSON TESTOROM

TECHNICAL MANUAL

PX-8

# INTRODUCTION

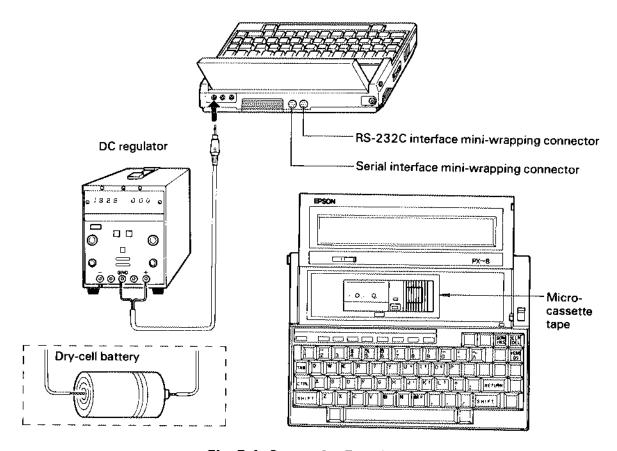

The EPSON PX-8 is a general-purpose portable computer driven by an incorporated rechargeable battery. Standard features include a micro cassette drive, ROM capsule and RS-232C interface allowing the machine to independently handle a variety of applications. The system can also be expanded by connecting peripheral equipment such as a printer. Long time steady operation has been realized by employing the battery-powered supply system with its large capacity of 1100 mAH. A recharge control circuit to protect the battery from overcharge and an auxiliary battery (90 mAH) for backup have been added to enhance reliability.

# **TABLE OF CONTENTS**

CHAPTER 1 GENERAL DESCRIPTION

CHAPTER 2 PRINCIPLES OF OPERATIONS

CHAPTER 3 OPTION (PRINCIPLES OF OPERATIONS)

CHAPTER 4 DISASSEMBLY/ASSEMBLY

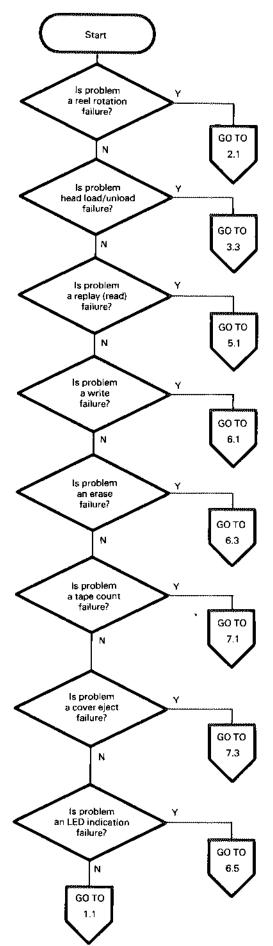

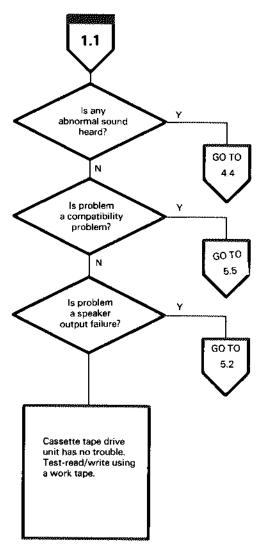

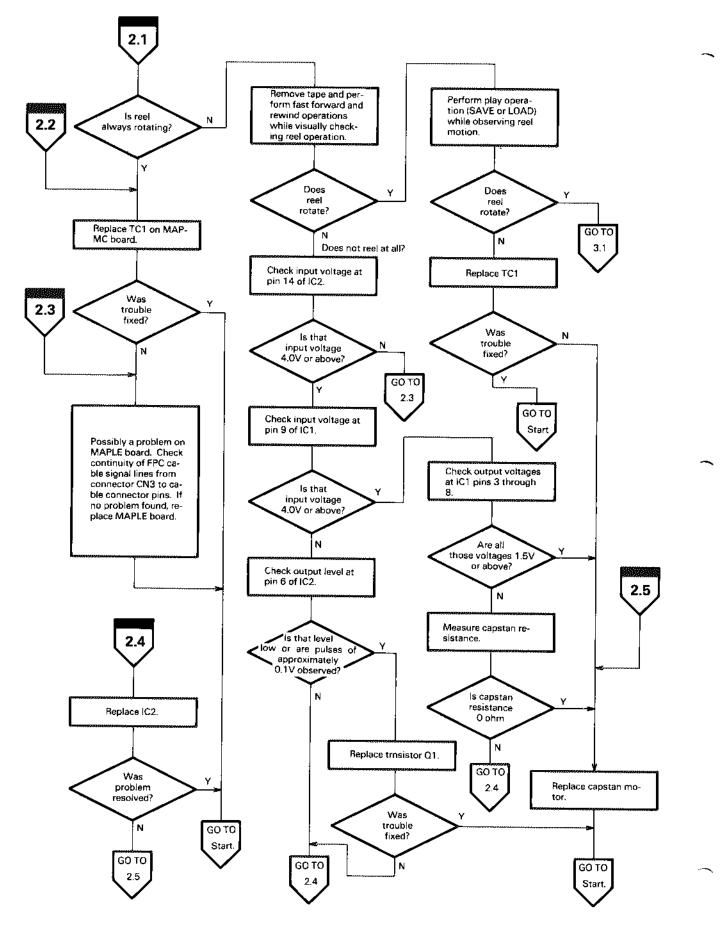

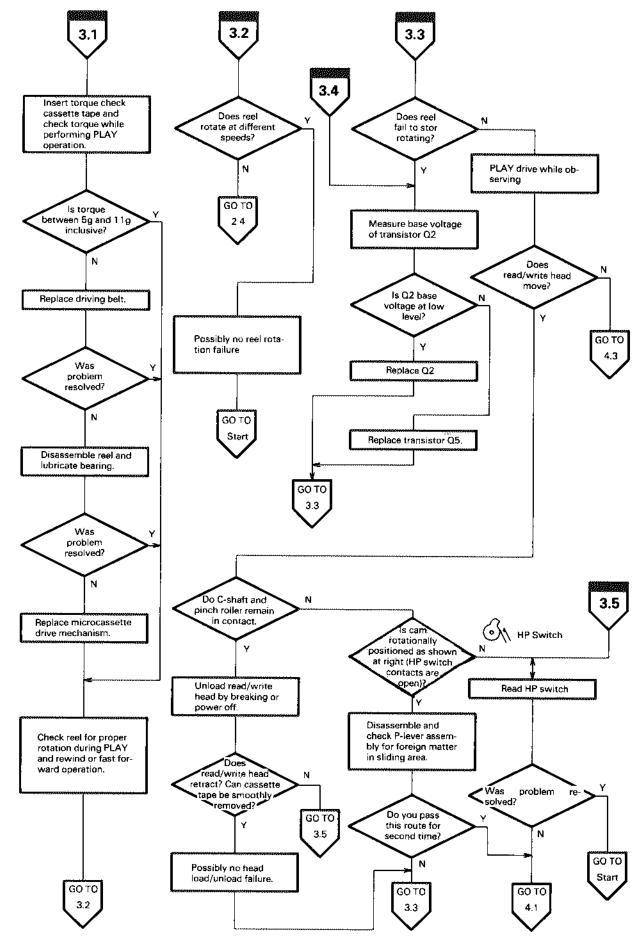

CHAPTER 5 TROUBLE SHOOTING

CHAPTER 6 MAINTENANCE

CHAPTER 7 APPENDIX

# CHAPTER 1 GENERAL DESCRIPTION

| 1.1 | Specifications            | 1-1  |

|-----|---------------------------|------|

| 1.2 | Name of Major Parts       | 1-4  |

| 1.3 | Major Parts               | 1-5  |

| 1,4 | Interface                 | 1-8  |

| 1.5 | Connection Cable (option) | 1-15 |

### 1.1 Specifications

(1) Dimension:

297 mm (width) × 216 mm (depth) × 4 7mm (height)

(2) Weight:

Approx. 2.3 kg

(3) Environment:

Operating

5 ~ 35°C

Recharging

5 ~ 35°C

Temperature Not operating

-20 ~ 60°C (below 30°C for a long period of time)

Storing data

0 ~ 40°C

(not operating)

Operating

10 ~ 80% (non-condensing)

Not operating

5 ~ 85% (non-condensing)

(4) Power:

• Consumption:

Approx. 325 mW (when micro cassette, speaker, ROM capsule,

RS-232C, SERIAL are not operating)

Battery:

Humidity

Two Ni-cd rechargeable batteries

|                  | Main battery | Auxiliary battery |

|------------------|--------------|-------------------|

| Voltage          | 4.8V         | 4.8V              |

| Capacity         | 1100 mAH     | 90 mAH            |

| Charging current | 330 mA MAX.  | 10 mA MAX.        |

| Charging voltage | 5.6 ~ 6.4V   | 5.7 ~ 6.0V        |

AC adapter output:

6 0V, 600 mA

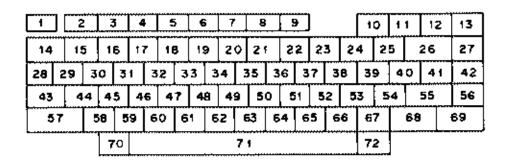

(5) Keyboard:

72 keys (include 9 function keys).

3 mode indication lamps

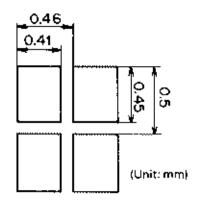

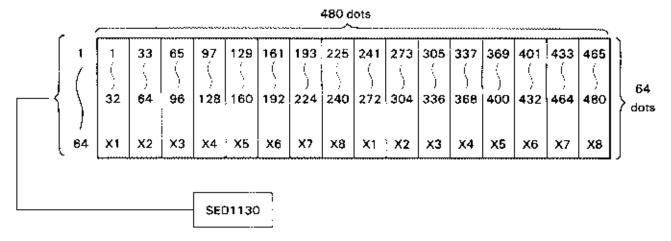

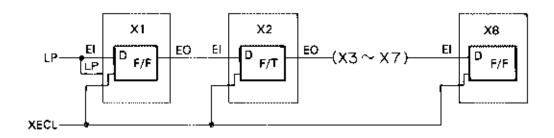

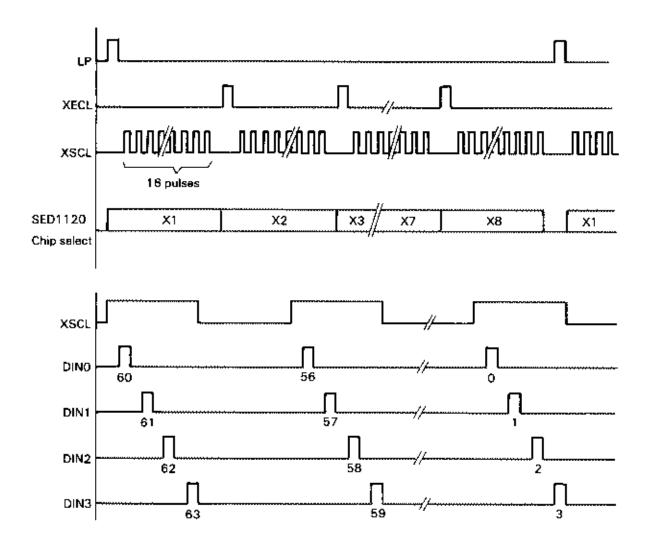

(6) LCD:

480 (width) × 64 (height) dots (80 × 8 characters per screen)

1/64 duty, adjustable VIEW ANGLE

(7) Microcassette™:

Tape speed

2.4 cm/s

Drive:

Center capstan

Track

Two-truck, one-channel

Frequency characteristic

315 ~ 4KHz

Data file

Sequential file with directory

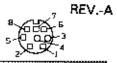

(8) Interface

RS-232C:

Connector

8-pin mini-DIN connector

Voltage

± 8V (ON/OFF control by software)

Transmission speed

75 ~ 19200 BPS

Mode

Full duplex/half duplex

SERIAL:

Connector

8-pin mini-DIN connector

Voltage

$\pm$  8V (ON/OFF control by software)

Transmission speed

150, 600, 4800, 38.4K BPS

Speaker:

Audio response controlled by software or by micro cassette

(with adjustable volume)

Analog input:

Input voltage

$0 \sim 2.0 V$

A/D converter

6-bit (Resolution: approx. 0.03V)

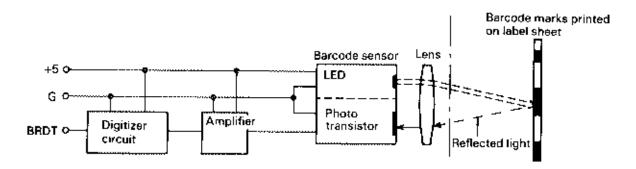

Bar code:

Can connect to high-resolution (0.19mm) or low-resolution

(0.33mm).

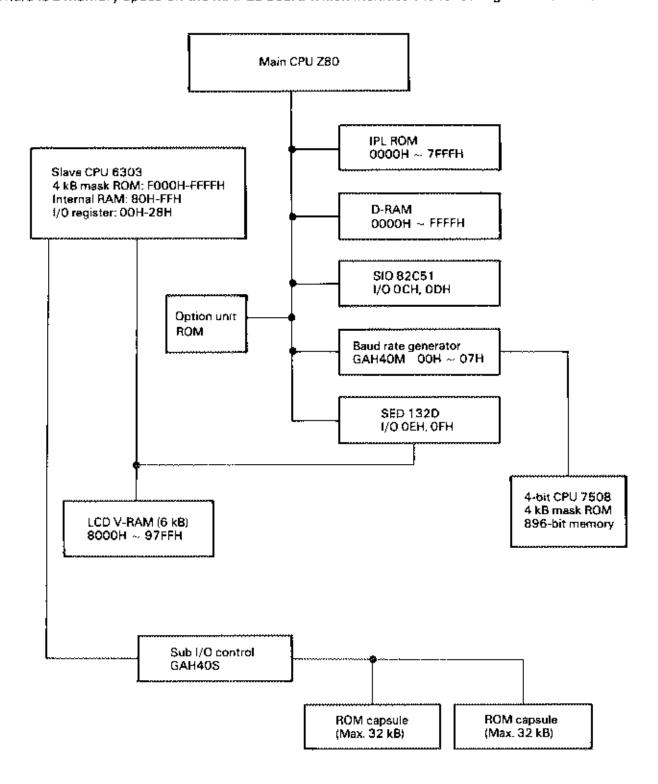

(9) CPU and memory

Main CPU:

2-80, 2.45MHz

Slave CPU:

6303, 614kHz

Auxiliary CPU:

7508, 200kHz (with battery backup)

Main RAM:

64kB D-RAM (with battery backup)

Video RAM:

6kB static RAM (with battery backup)

ROM:

32kB

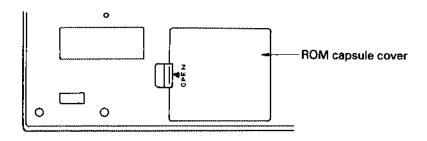

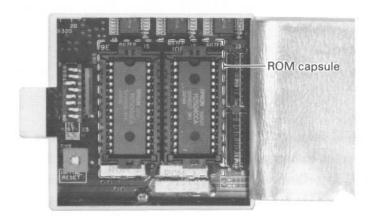

ROM capsule:

Two capsules can be incorporated.

(8 ~ 32kB per capsule)

#### 1.1.1 Available models

The following models are available for this computer. However, major differences among these models are restricted to keyboard and AC adaptor specifications, the internal hardware is the same.

Table 1-1

| Model    | Keyboard        | AC adaptor                                                        |

|----------|-----------------|-------------------------------------------------------------------|

| H101A AA | ASCII (U.S.A.)  | H00AAA: 120V 60 Hz                                                |

| H101A AC | ASCII           | H00AAA: 120V 60 Hz, H00AAU-B: 240V 50 Hz,<br>H00AAU-A: 240V 50 Hz |

| H101A BA | HASCII (U.S.A.) | H00AAA: 120V 60 Hz                                                |

| H101A UA | England         | H00AAU-A: 240V 50 Hz                                              |

| H101A FA | France          | H00AAF: 220V 50 Hz                                                |

| H101A GA | Germany         | H00AAG: 220V 50 Hz                                                |

| H101A SA | Sweden          | H00AAG: 220V 50 Hz                                                |

| H101A DA | Denmark         | H00AAG: 220V 50 Hz                                                |

| H101A NA | Norway          | H00AAG: 220V 50 Hz                                                |

### 1.1.2 Specifications of option

Optional features are summarized in the table below. They provide you with system expansion to meet your specific demands or flexible system configuration by using universal option.

Table 1-2

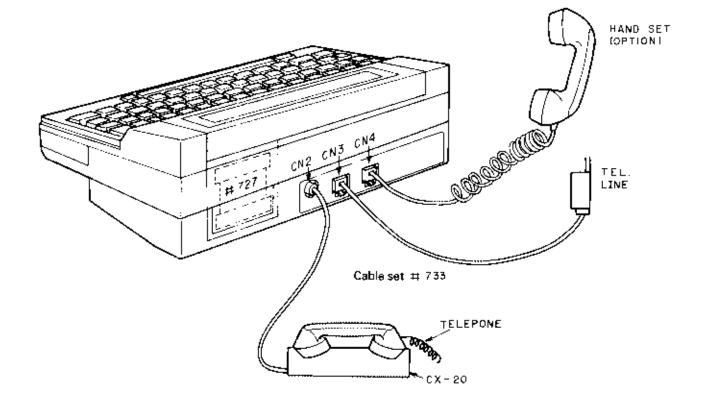

| Nam <del>e</del>                          | Application/Description                                                                   |

|-------------------------------------------|-------------------------------------------------------------------------------------------|

| #723 cable For floppy disk drive (serial) |                                                                                           |

| #724 cable                                | For acoustic coupler (RS-232C)                                                            |

| #725 cable                                | For printer (RS-232C)                                                                     |

| #726 cable                                | Null modem (for interconnection between two EPSON PX-8 computers via RS-232C interfacing) |

| CX-20/21                                  | Acoustic coupler                                                                          |

| PF-10                                     | 3.5 inch floppy disk drive                                                                |

| TF-15/TF-20                               | 5.25 inch floppy disk drive                                                               |

| RAM DISK UNIT                             | Additional 120/60 kB RAM                                                                  |

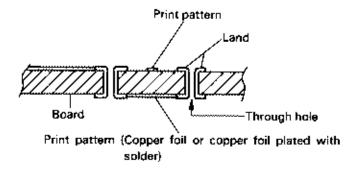

| UNIVERSAL UNIT                            | A through-hole circuit board and a case                                                   |

| MODEM UNIT                                | Built-in modem (for U.S.A. only)                                                          |

| MULTI UNIT                                | RAM + MODEM (for U.S.A. only)                                                             |

| EPSON PRINTER                             | Verious models with RS-232C interface                                                     |

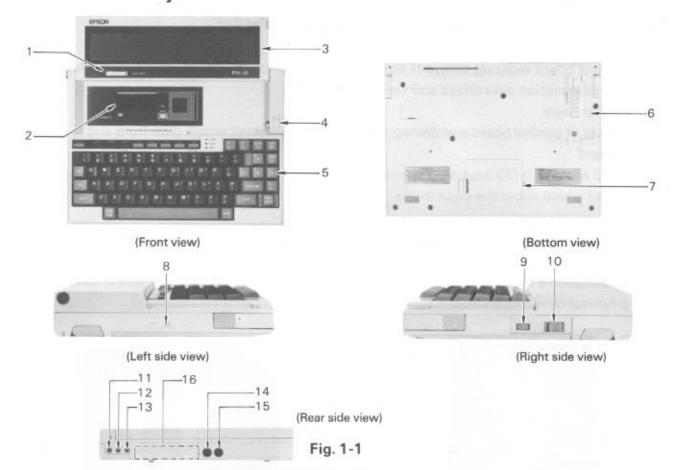

# 1.2 Names of Major Parts

Table 1-3 Major Component

| No. | Name                                                                    |

|-----|-------------------------------------------------------------------------|

| 1   | VIEW ANGLE VOLUME (adjustable view angle due to temperature complement) |

| 2   | Microcassette (program load/save and sound generation)                  |

| 3   | LCD panel unit                                                          |

| 4   | LCD panel open switch                                                   |

| 5   | Keyboard unit                                                           |

| 6   | Battery cover (to replace main battery)                                 |

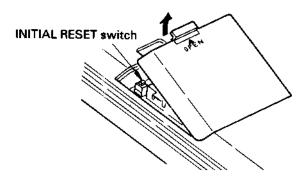

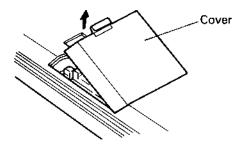

| 7   | ROM cartridge cover (for replacement of ROM capsule, and INITIAL RESET) |

| 8   | Reset switch                                                            |

| 9   | Speaker volume (internal/external speaker volume adjustment)            |

| No. | Name                                                                 |  |

|-----|----------------------------------------------------------------------|--|

| 10  | Power switch                                                         |  |

| 11  | Speaker output (for external speaker)                                |  |

| 12  | Analog input interface (analog input/joystick)                       |  |

| 13  | Bar code reader interface                                            |  |

| 14  | RS-232C interface (for connection to acoustic coupler/printer, etc.) |  |

| 15  | High-speed serial interface (for connection to floppy disk drive)    |  |

| 16  | Expansion interface (for connection to optional unit/universal unit) |  |

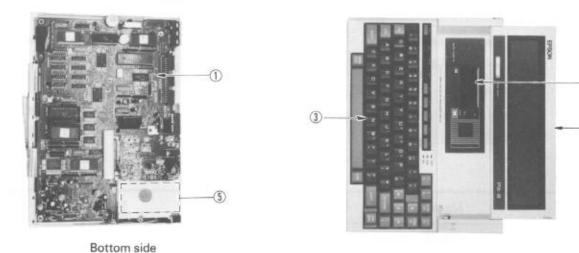

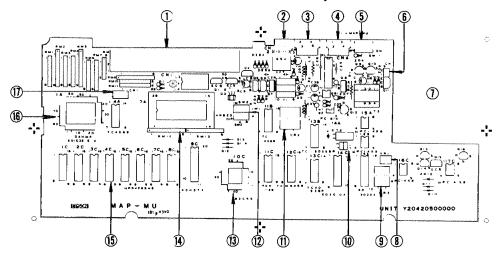

## 1.3 Major parts

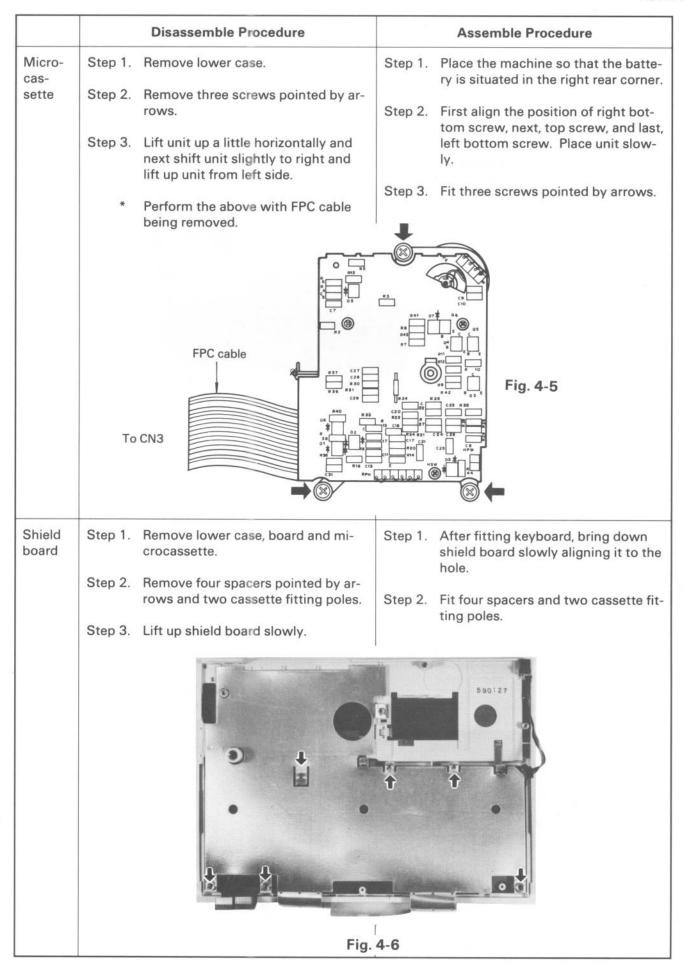

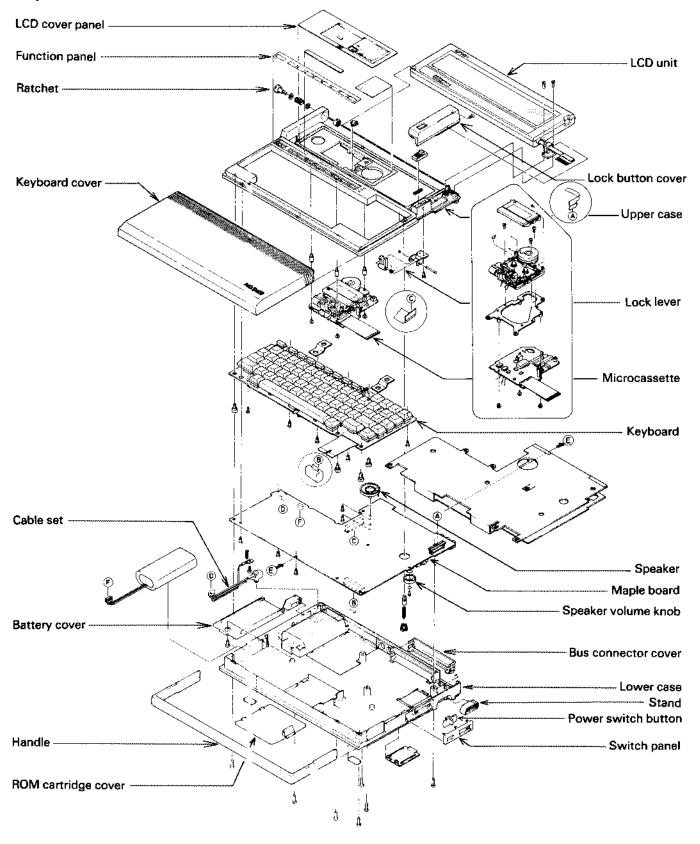

The main unit consists of five parts and a case as shown in Fig. 1-2.

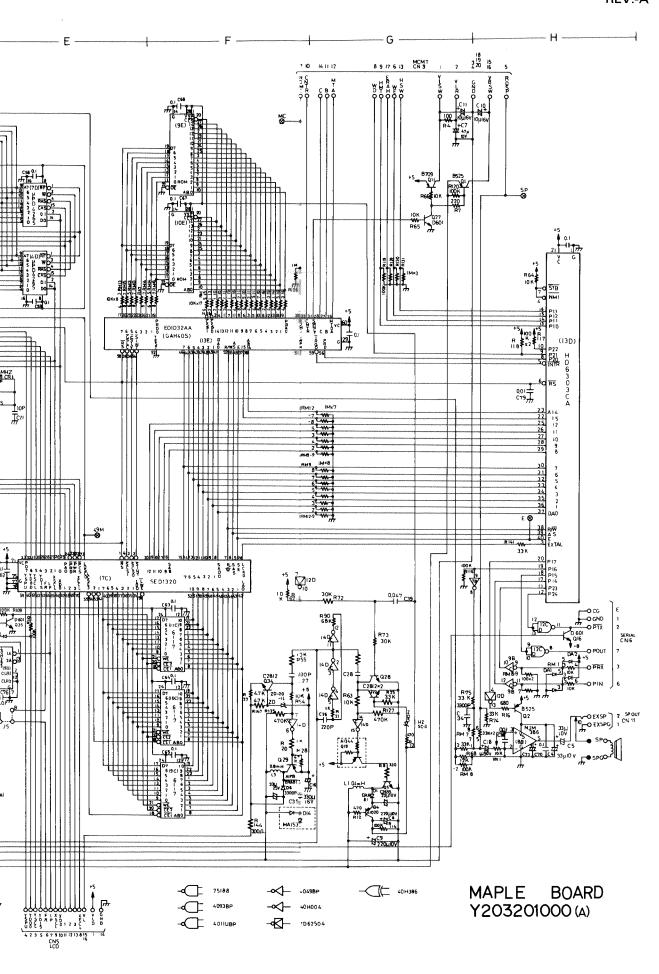

1 MAPLE board

A control board realizing compact size and low power consumption with CMOS, flat package type multifunction gate arrays and various chips on it.

Micro cassette

Consists of control board and driving mechanism. Reads and writes data from and to the tape.

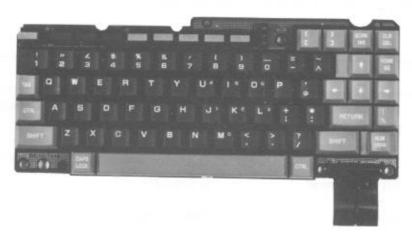

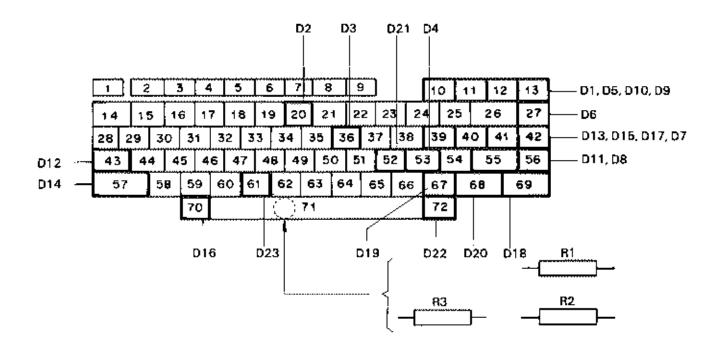

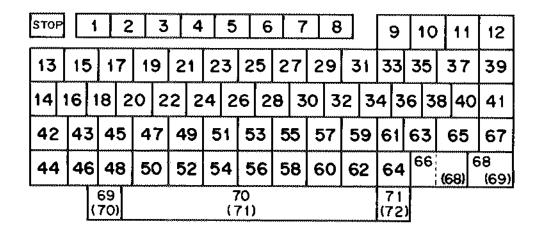

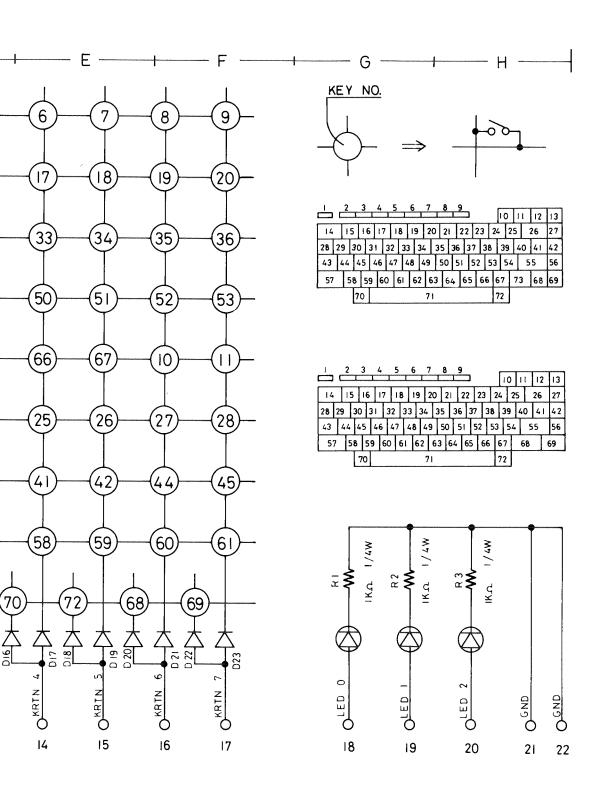

3 Keyboard

Has 72 keys on it (73 keys for Japanese use), 9 of which are function keys. Also has three indicators which show the input mode.

4 LCD

Consists of 480 (width) x 64 (height) dots, can display a total of 480 characters.

⑤ Main battery

A rechargeable Ni-cd battery with a capacity of 1100 mAH. It supplies power necessary for the normal circuit operation.

Fig. 1-2

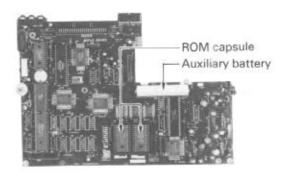

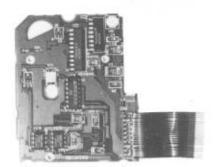

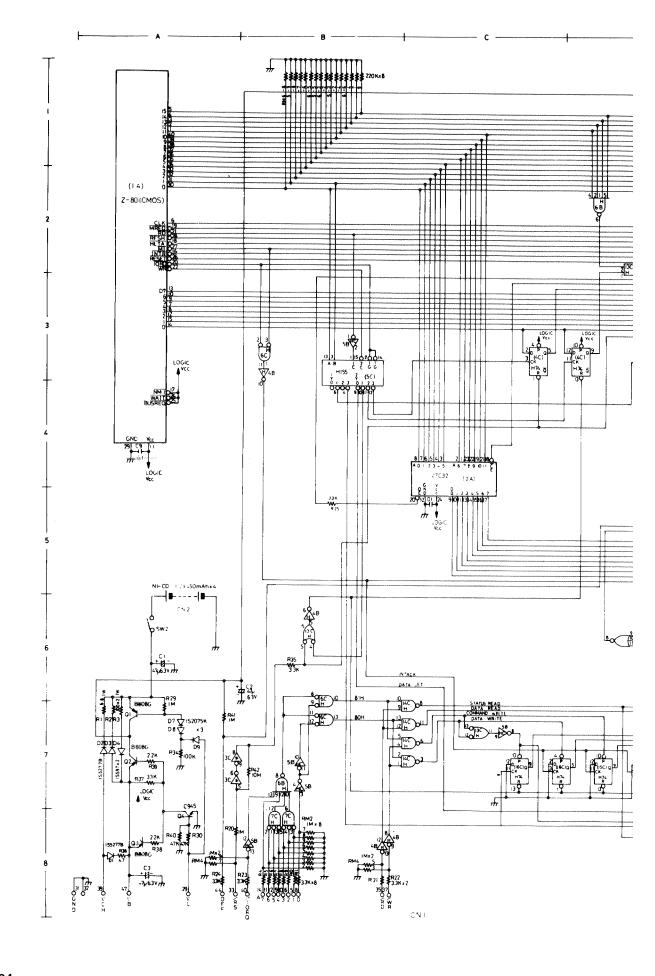

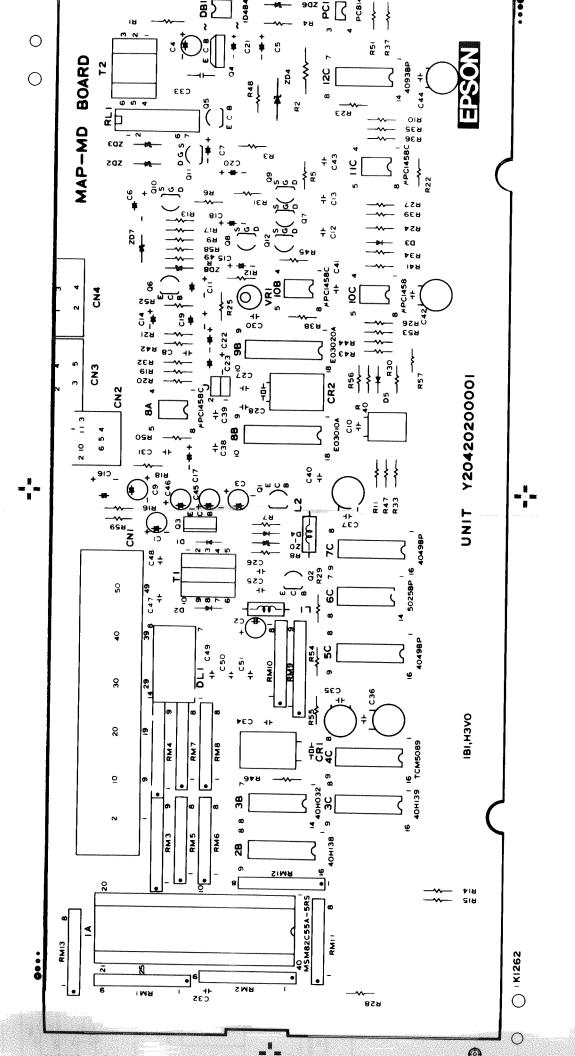

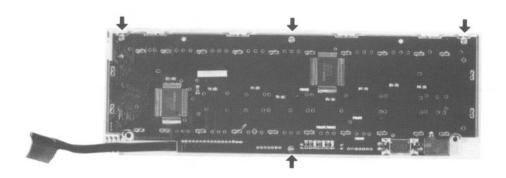

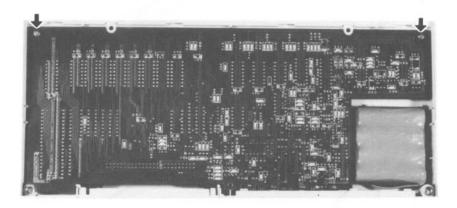

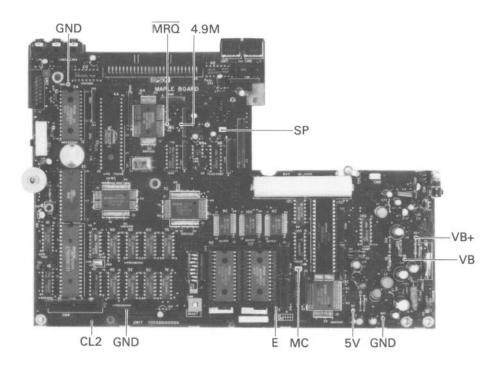

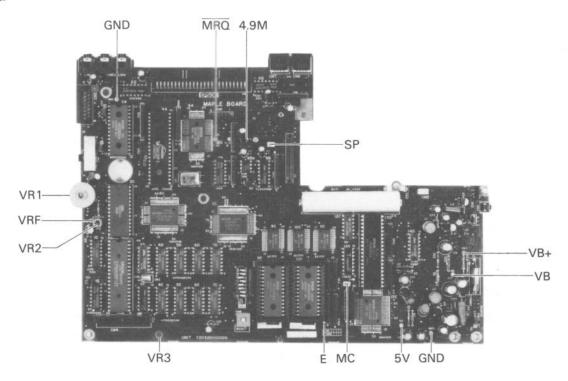

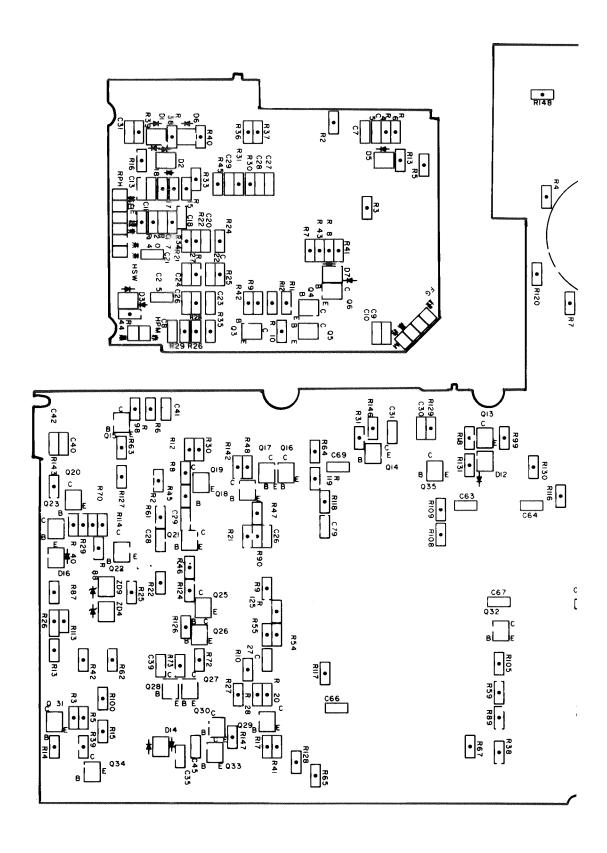

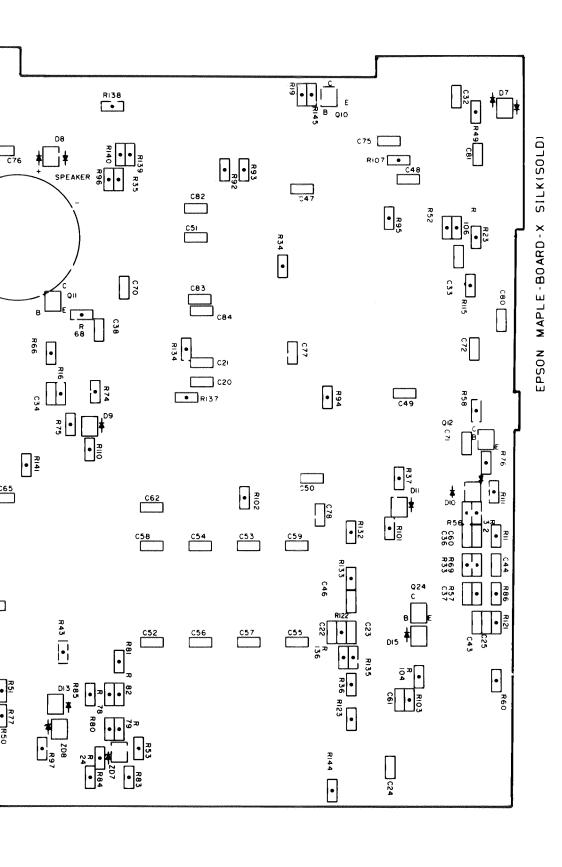

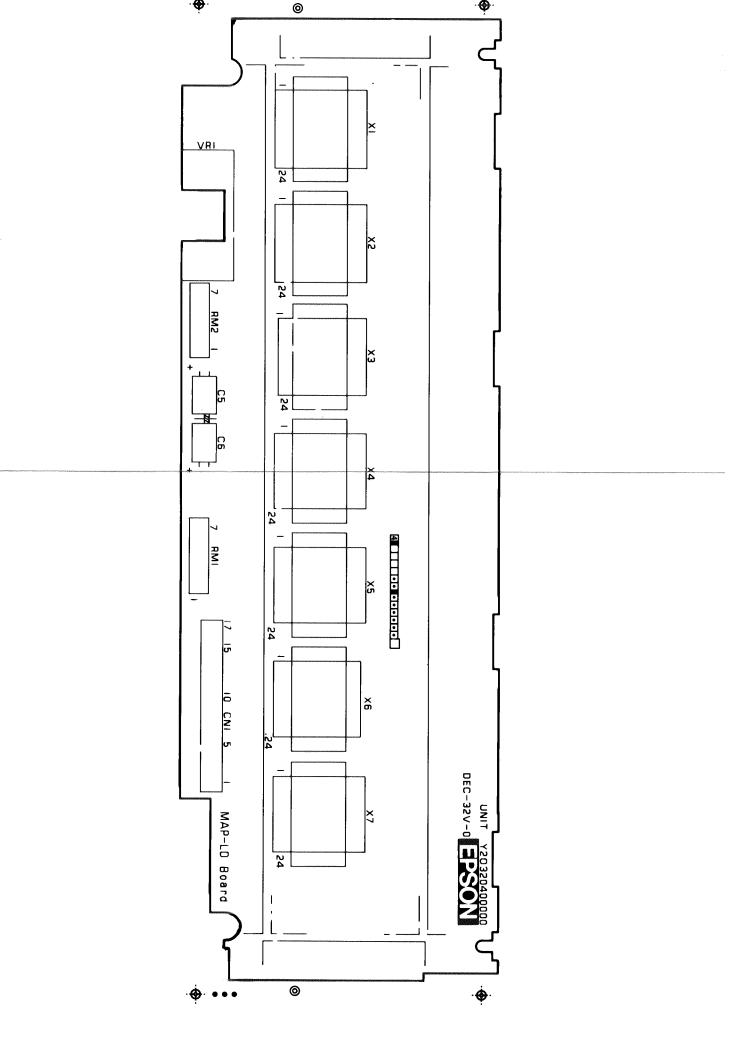

#### 1.3.1 MAPLE board

Power consumption is considerably reduced by employing power-saving C-MOS. On-board integration has become easy by employing customized LSIs and chips. Although both sides of the boards are utilized, the back side mainly includes chips such as resistors and capacitors.

Front view

(2)

Rear view

Fig. 1-3

External interfaces (shown in Table 1-4) and two ROM capsules on the board provide a system configuration suitable for your needs or implementation of an application program. An auxiliary rechargeable battery of 90 mAH is also incorporated which supplies power in order to ensure normal circuit operation when the voltage of the main battery falls down below a certain value.

Table 1-4 External Interfaces

| Item             | Function                                | Note                                                     |

|------------------|-----------------------------------------|----------------------------------------------------------|

| RS-232C          | 110 ~ 19200 BPS,<br>RS-232C level       | Operator-selectable: transmission speed, X-ON/OFF, etc., |

| SERIAL           | 38400 BPS MAX.,<br>RS-232C level        | Operator-selectable: transmission speed, X-ON/OFF, etc., |

| Bar code         | Read at TTL level                       | Read program and bar code reader are required.           |

| Analog input     | Analog or joystick input (with trigger) | Analog input line has +5V pull up function.              |

| External speaker | 0 ~ 6V output                           | 8Ω 0.2W                                                  |

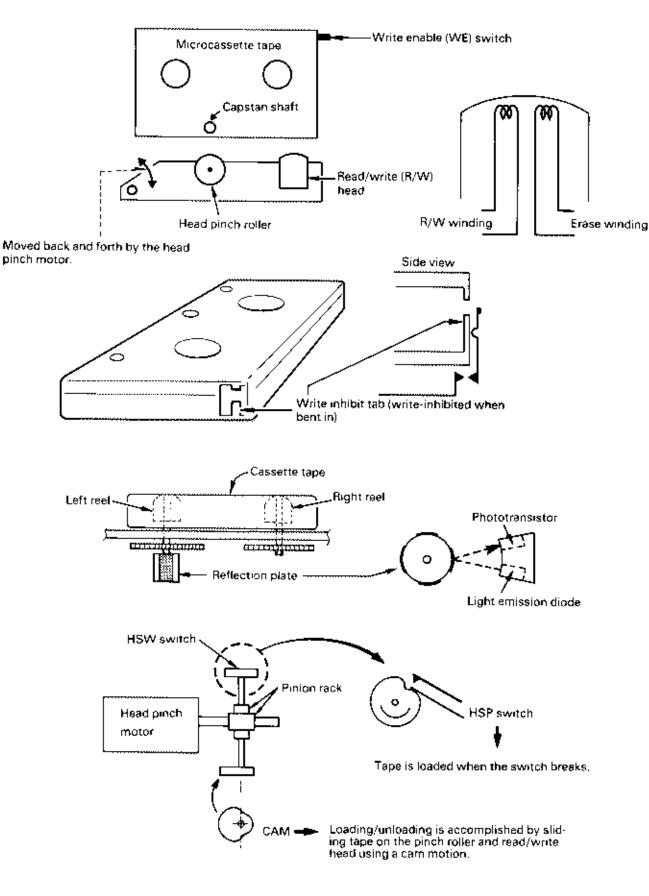

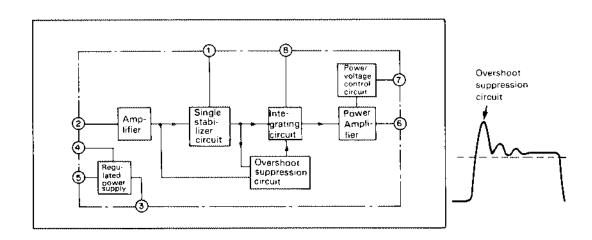

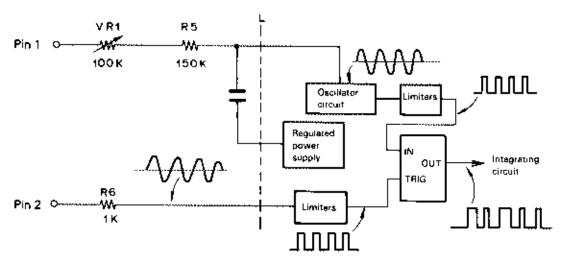

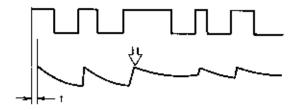

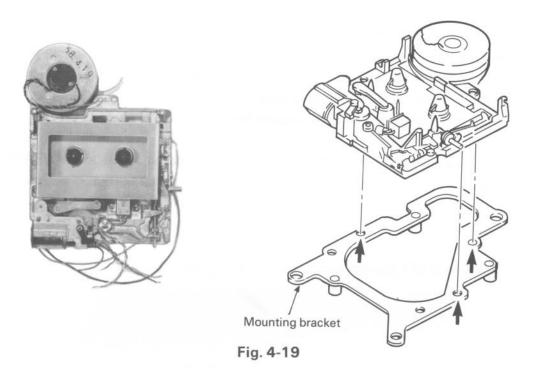

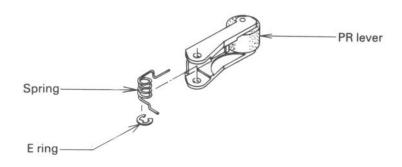

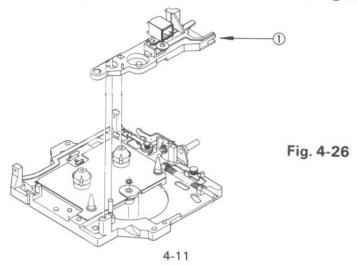

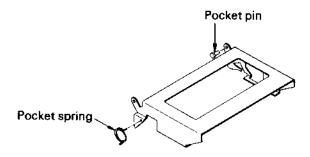

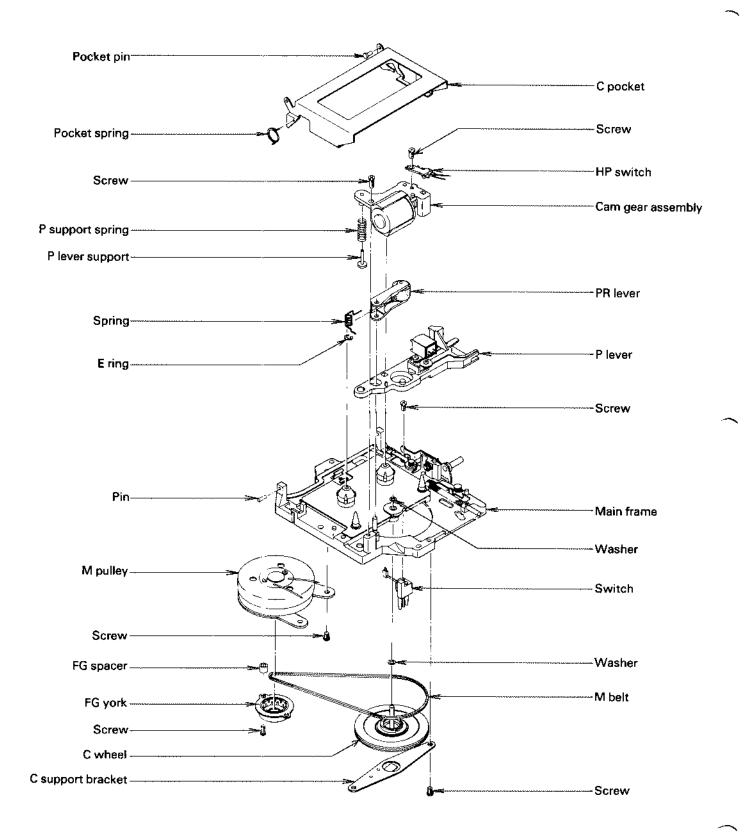

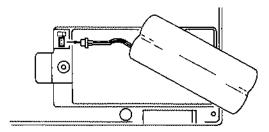

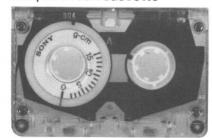

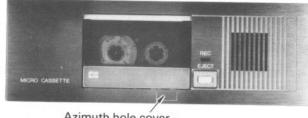

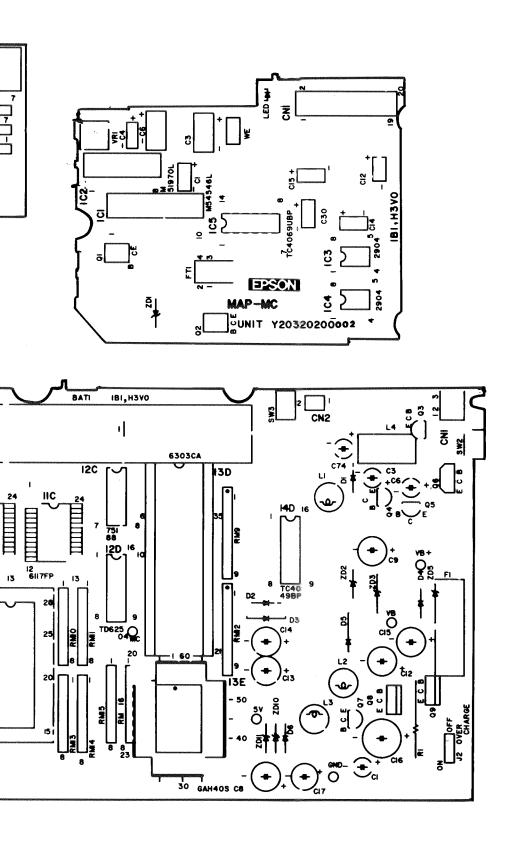

#### 1.3.2 Microcassette

The microcassette consists of a control board and drive mechanism. Operations such as FF, REW, etc. are controlled by software, resulting in high reliability compared with manual control. Increased chip implimentation has permitted a reduction in size of the control board.

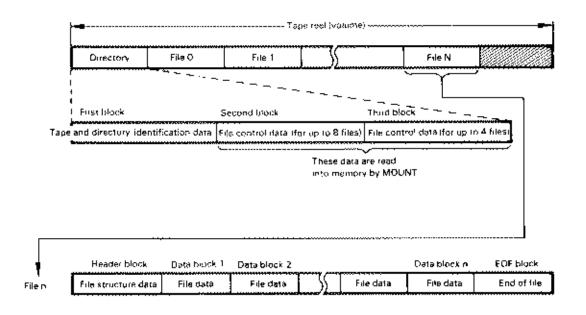

This cassette drive operates at a tape speed of 2.4 cm/s, and reads or writes data effectively utilizing a tape counter and directory which contains file names, file starting addresses, etc.

Fig. 1-4

Mechanical components include a tape drive motor and its driving mechanism, R/W heads and their mechanisms, reels, etc. The control board controls the revolving speed of motor, load/unload of R/W heads and R/W operation.

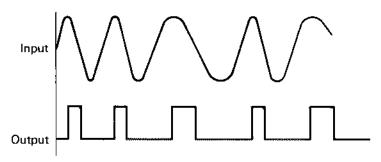

To enable sound output, it provides signals to an internal or external speaker after amplifying them twice. For reading data, duplicated amplification circuits eliminate high frequency component (noise) and detect the peak of signal to ensure highly reliable sound output.

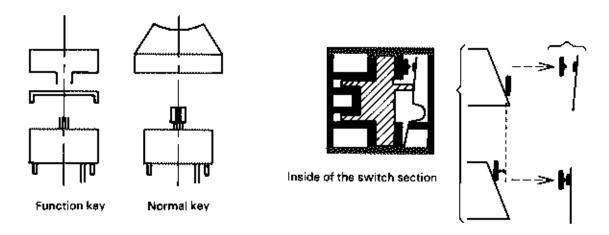

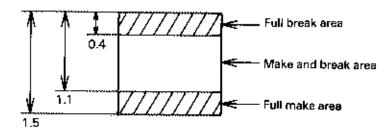

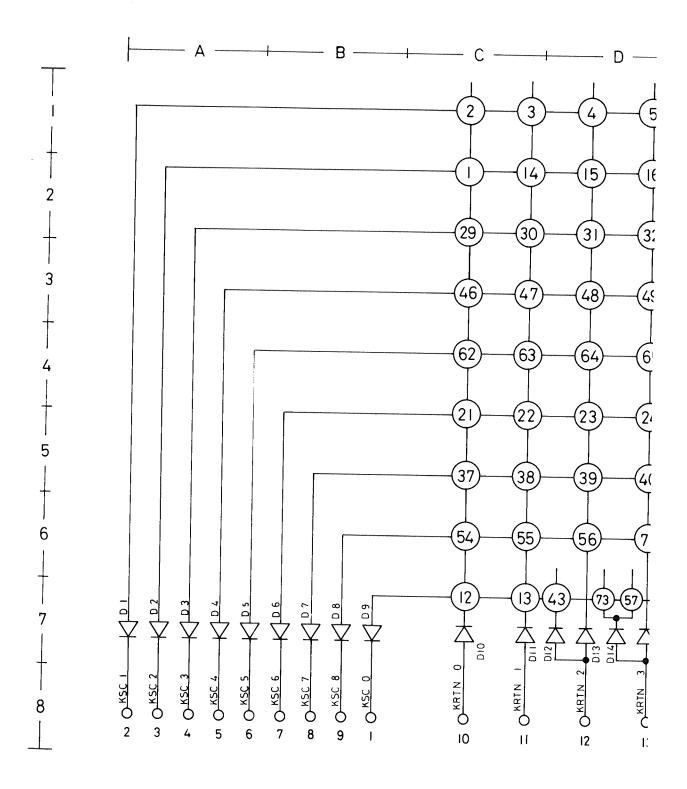

#### 1.3.3 Keyboard

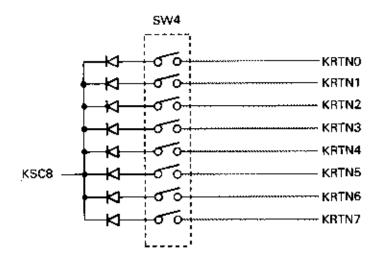

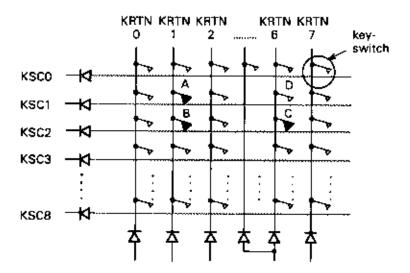

Matrix keyboard uses mechanical contact switches. Switches, reverse-current protection diode and mode indication LED lamps are implemented on the control board.

Fig. 1-5

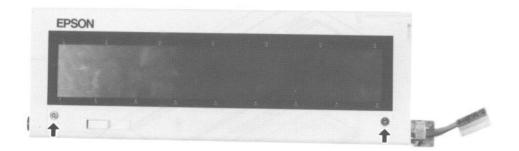

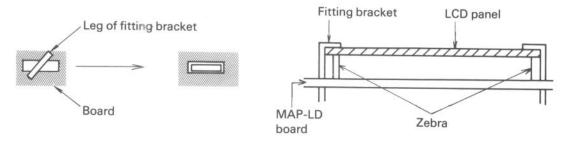

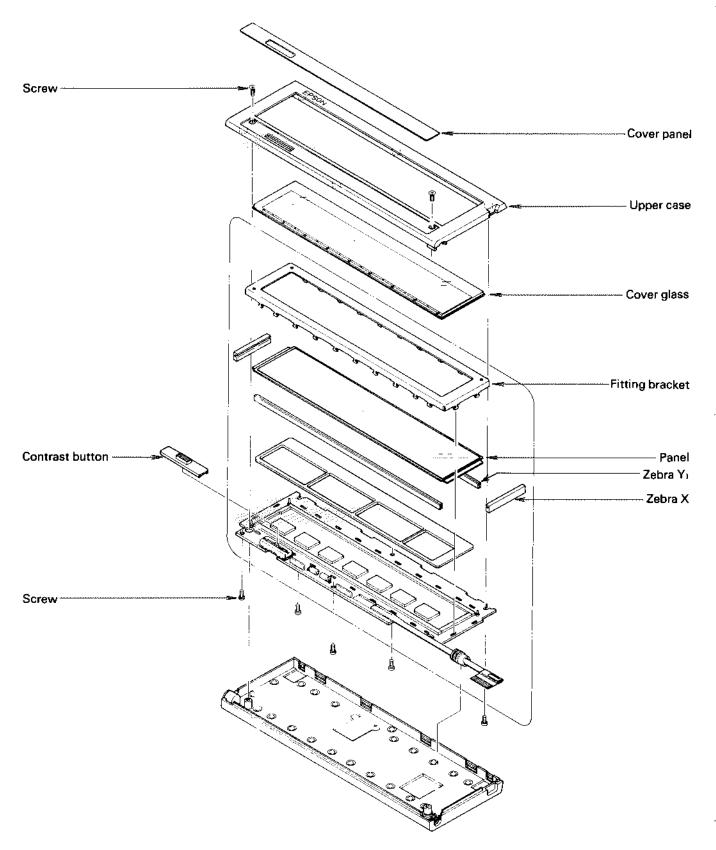

#### 1.3.4 LCD

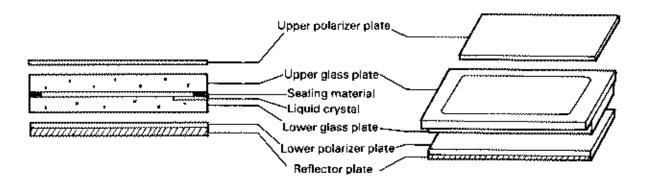

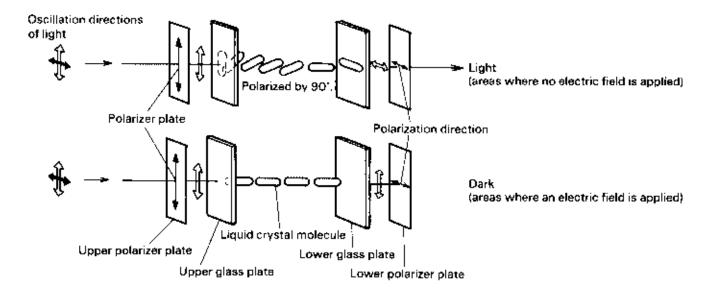

The LCD is a twist pneumatic (TNM) effect type liquid-crystal display. The screen angle can be changed arbitrarily. VIEW ANGLE volume is provided to correct the change of liquid crystal display condition caused by temperature rise or fall.

Fig. 1-6

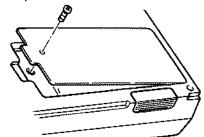

#### 1.3.5 Main battery

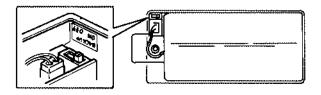

The main battery is Ni-Cd with a nominal voltage of 4.8V. When the battery is fully charged, the voltage is 5.0V or more, enough to provide power for circuit operation. The battery can be easily removed and replaced by removing the battery cover on the bottom of the unit.

Fig. 1-7

## 1.4 Interface

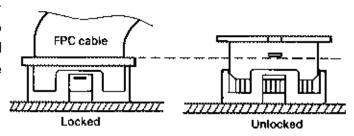

As shown in Table 1-3, the unit has eleven connectors: among them, CN3, CN4 and CN5 have a slide-lock mechanism.

Table 1-5 Interface Connectors

| Name | Number<br>of pins | Function                             |  |

|------|-------------------|--------------------------------------|--|

| CN1  | 3                 | AC adapter connection interface      |  |

| CN2  | 2                 | Main battery connection interface    |  |

| CN3  | 20                | Incorporated microcassette interface |  |

| CN4  | 22                | Keyboard interface                   |  |

| CN5  | 16                | LCD interface                        |  |

| CN6  | 8                 | High speed serial interface          |  |

| CN7  | 8                 | RS-232C interface                    |  |

| CN8  | 50                | Expansion interface                  |  |

| CN9  | 3                 | Bar code reader interface            |  |

| CN10 | 3                 | Analog input interface               |  |

| CN11 | 2                 | External speaker interface           |  |

Note: CN5 is integrated on the back of MAPLE board.

Table 1-6 CN1 (AC Adaptor) Pin Assignments

| Pin No. | Signal name | Definition       |

|---------|-------------|------------------|

| 1       | VCH         | Charging voltage |

| 2       |             | Undefined        |

| 3       | GND         | Ground           |

Table 1-7 CN2 (Battery Connection) Pin Assignments

| Pin No. | Signal Name | Definition           |

|---------|-------------|----------------------|

| 1       | VB          | Main battery voltage |

| 2       | GND         | Ground               |

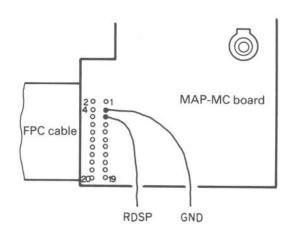

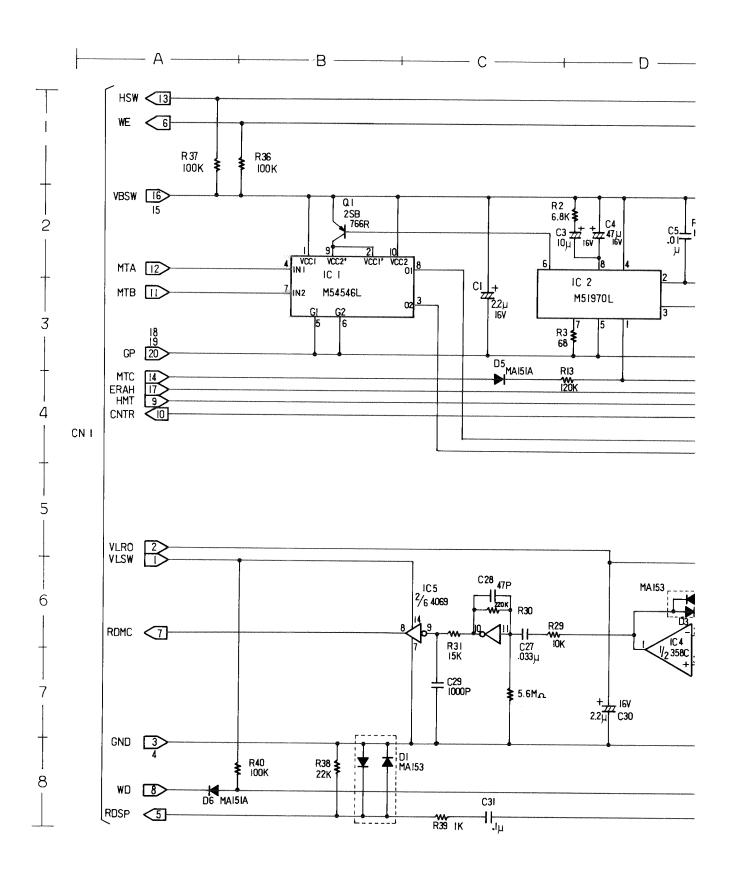

# Table 1-8 CN3 (Incorporated Microcassette) Pin Assignments

| Pin No.    | Signal Name | Definition                                      |

|------------|-------------|-------------------------------------------------|

| 1          | VLSW        | Circuit voltage supply (through read gate)      |

| 2          | VLR         | Circuit voltage supply (read amp. power supply) |

| 3, 4       | GND         | Ground                                          |

| 5          | RDSP        | Sound output of read data                       |

| 6          | WE          |                                                 |

| 7          | RDMC        | Read signal                                     |

| 8          | WD          | Write data                                      |

| 9          | нмт         | Head pinch motor control                        |

| 10         | CNTR        | Counter                                         |

| <b>1</b> 1 | мт в        | Capstan motor drive control                     |

| 12         | MTA         | Capstan motor drive control                     |

| 13         | HSW         | Head switch status                              |

| 14         | MTC         | Capstan motor speed control                     |

| 15, 16     | VBSW        | Battery voltage supply (for motor)              |

| 17         | ERAH        | Erase signal                                    |

| 18, 19, 20 | GND         | Ground                                          |

Table 1-8 CN3 (Incorporated Microcassette) Pin Assignments

| Pin No.    | Signal Name | Definition                                      |

|------------|-------------|-------------------------------------------------|

| 1          | VLSW        | Circuit voltage supply (through read gate)      |

| 2          | VLR         | Circuit voltage supply (read amp. power supply) |

| 3, 4       | GND         | Ground                                          |

| 5          | RDSP        | Sound output of read data                       |

| 6          | WE          |                                                 |

| 7          | RDMC        | Read signal                                     |

| 8          | WD          | Write data                                      |

| 9          | нмт         | Head pinch motor control                        |

| 10         | CNTR        | Counter                                         |

| <b>1</b> 1 | мт в        | Capstan motor drive control                     |

| 12         | MTA         | Capstan motor drive control                     |

| 13         | HSW         | Head switch status                              |

| 14         | MTC         | Capstan motor speed control                     |

| 15, 16     | VBSW        | Battery voltage supply (for motor)              |

| 17         | ERAH        | Erase signal                                    |

| 18, 19, 20 | GND         | Ground                                          |

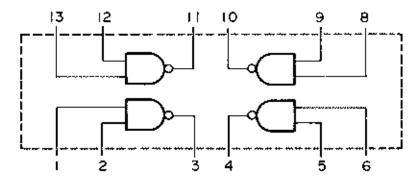

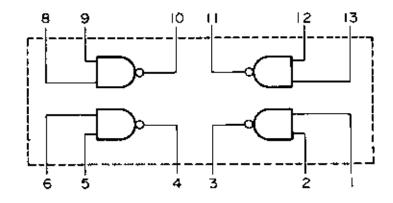

Table 1-9 CN4 (Keyboard Interface) Pin Assignments

| Pin No. | Signal Name | Definition        |

|---------|-------------|-------------------|

| 1       | KSC 0       | Key scan signal   |

| 2       | KSC 1       | Key scan signal   |

| 3       | KSC 2       | Key scan signal   |

| 4       | KSC 3       | Key scan signal   |

| 5       | KSC 4       | Key scan signal   |

| 6       | KSC 5       | Key scan signal   |

| 7       | KSC 6       | Key scan signal   |

| 8       | KSC 7       | Key scan signal   |

| 9       | KSC 8       | Key scan signal   |

| 10      | KRTN 0      | Key return signal |

| 11      | KRTN 1      | Key return signal |

| 12      | KRTN 2      | Key return signal |

| 13      | KRTN 3      | Key return signal |

| 14      | KRTN 4      | Key return signal |

| 15      | KRTN 5      | Key return signal |

| 16      | KRTN 6      | Key return signal |

| 17      | KRŤN 7      | Key return signal |

| 18      | LED 0       | CAPS LOCK MODE    |

| 19      | LED 1       | NUMERIC MODE      |

| 20      | . LED 2     | INSERT MODE       |

| 21, 22  | GND         | Ground            |

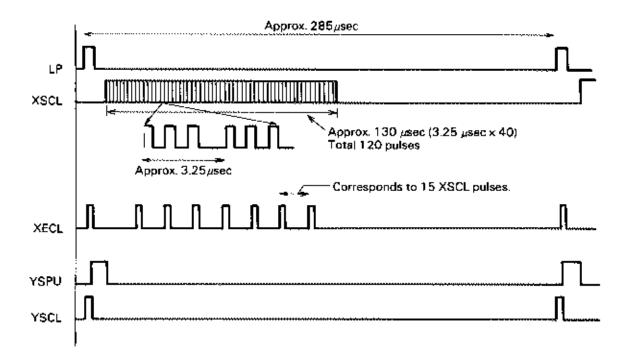

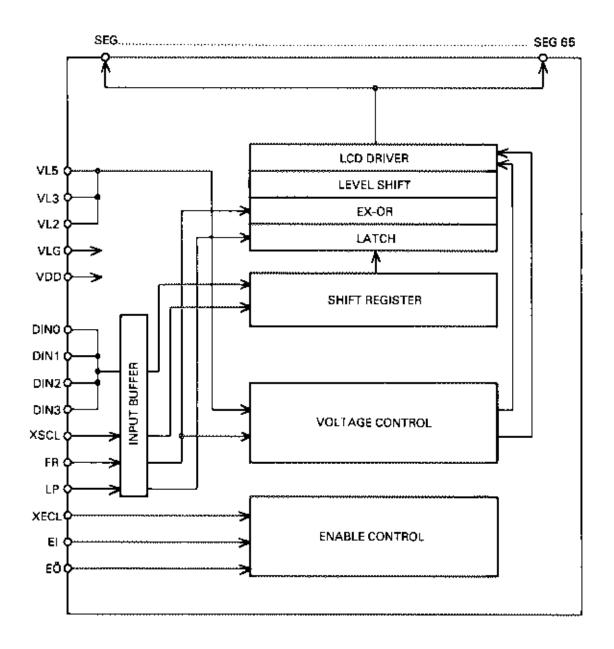

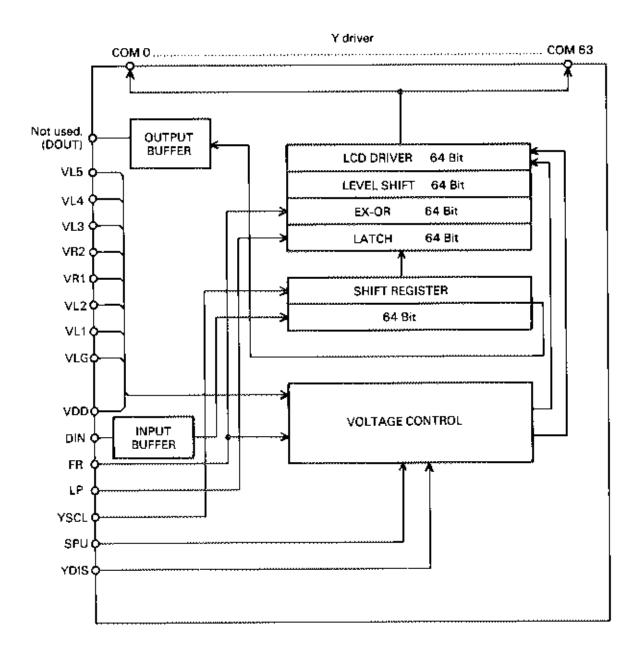

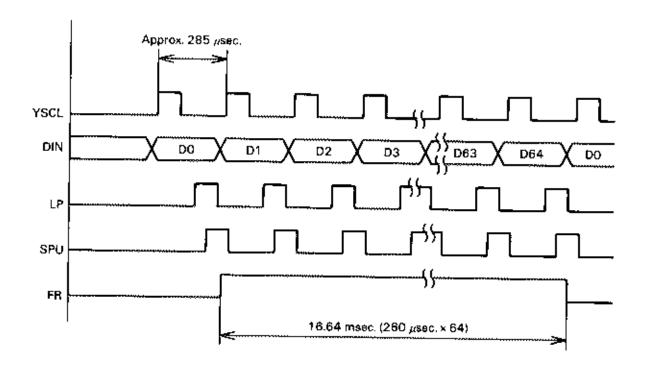

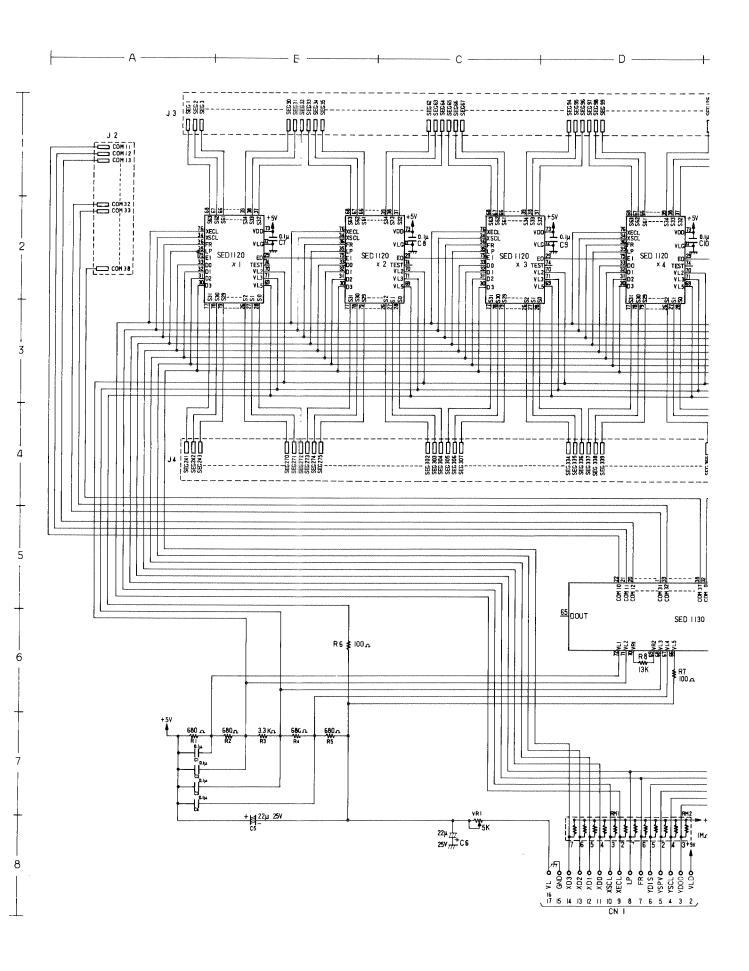

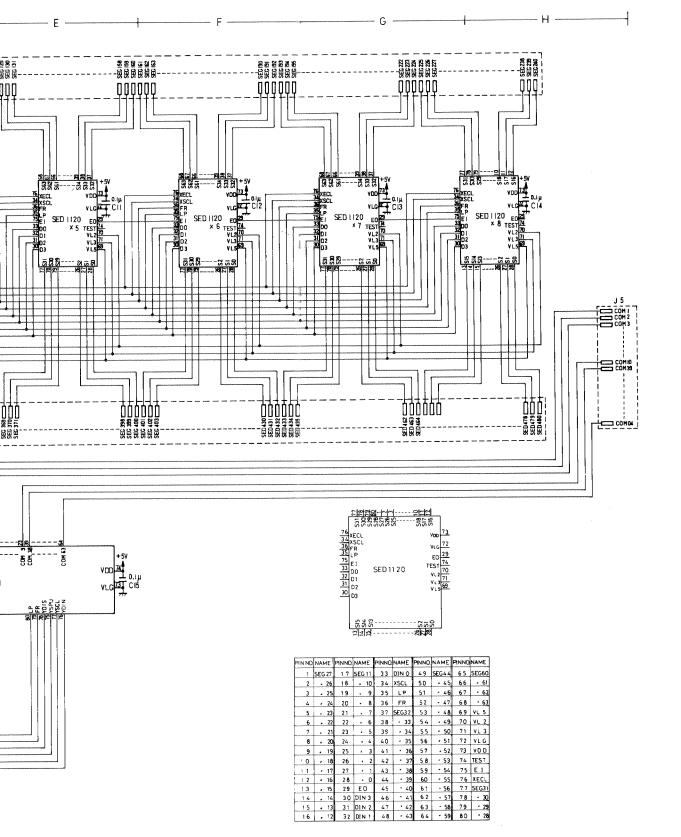

## Table 1-10 CN5 (LCD Interface) Pin Connections

| Pin No. | Signal Name | Definition          |

|---------|-------------|---------------------|

| 1       | VLD         | Circuit voltage: +5 |

| 2       | YDO         | Y data              |

| 3       | YSCL        | Y shift clock       |

| 4       | YSPU        | Speed up signal     |

| 5       | YDIS        | Y display signal    |

| 6       | FS          | Frame signal        |

| 7       | LP          | Latch pulse signal  |

| 8       | XECL        | X enable clock      |

| 9       | XSCL        | X shift clock       |

| 10      | XD0         | X data 0            |

| 11      | XD1         | X data 1            |

| 12      | XD2         | X data 2            |

| 13      | XD3         | X data 3            |

| 14      | GND         | Signal ground       |

| 15, 16  | · VL        | Circuit voltage     |

<sup>\*</sup> View from the rear side of the board.

Table 1-11 CN6 (High Speed Serial Interface) Pin Connections

| Pin No. | Signal Name | Definition             |

|---------|-------------|------------------------|

| 1       | GND         | Signal ground          |

| 2       | PTX         | Transmit data (output) |

| 3       | PRX         | Receiving data (input) |

| 6       | PIN         | Receiving mode (input) |

| 7       | POUT        | Transmit mode (output) |

| E       | FG          | Chassis ground         |

# Table 1-12 CN7 (RS-232C Interface) Pin Assignments

| Pin No. | Signal Name | Definition                   |

|---------|-------------|------------------------------|

| 1       | GND         | Signal ground                |

| 2       | TXD         | Transmit data (output)       |

| 3       | RXD         | Receiving data (input)       |

| 4       | RST         | Request-to-send (output)     |

| 5       | CTS         | Clear-to-send (input)        |

| 6       | DSR         | Data set ready (output)      |

| 7       | DTR         | Data terminal ready (output) |

| 8       | CD          | Carrier detect               |

| E       | FG          | Chassis ground               |

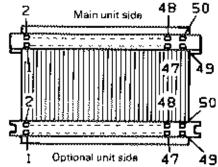

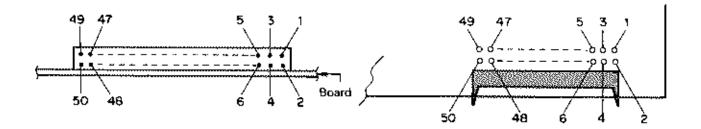

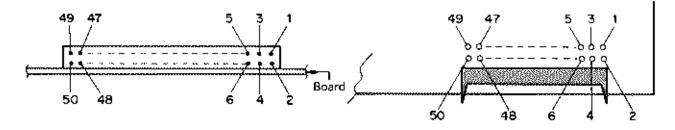

Table 1-13 CN8 (Expansion) Interface

| 49<br>[3 | Ξ   | = | == | Ξ | =   | Ξ | = | = | = | = | Ξ | Ξ | Ξ | : | ÷ | ĕ | 51<br>2 |   |   |

|----------|-----|---|----|---|-----|---|---|---|---|---|---|---|---|---|---|---|---------|---|---|

| 50       | *** | - |    | ^ | ••• | ~ | ~ |   | - |   |   | - | - |   | - | - | 47      | _ | - |

| Pin<br>No. | Signal<br>Name | Direction | Definition            |

|------------|----------------|-----------|-----------------------|

| 1          | AB12           | 0         | Address bus *2        |

| 3          | AB14           | 0         | Address bus 14        |

| 5          | AB 1           | 0         | Address bus 1         |

| 7          | AB15           | 0         | Address bus 15        |

| 9          | AB 4           | O         | Address bus 4         |

| 11         | AB 6           | 0         | Address bus 1         |

| 13         | AB10           | 0         | Address bus 10        |

| 15         | AB 8           | 0         | Address bus 8         |

| 17         | DB 0           | 1/0       | Data bus 0            |

| 19         | DB 2           | 1/0       | Data bus 2            |

| 21         | DB 4           | 1/0       | Data bus 4            |

| 23         | DB 6           | 1/0       | Dat bus 6             |

| 25         | BURQ           | 0         | : Bus request         |

| 27         | Μī             | 0         | Machine cycle 1       |

| 29         | VL             | 0         | Circuit voltage: +5V  |

| 31         | GND            | _         | Signal ground         |

| 33         | RŠ             | O         | Reset                 |

| 35         | RD             | 0         | Read                  |

| 37         | WŔ             | 0         | Write                 |

| 39         | VCH            | 0         | Charging voltage      |

| 41         | DCAS           | 0         | Data CAS              |

| 43         | INTEX          | I ,       | External interruption |

| 45         | RXD            | ı         | Serial received data  |

| 47         | VB1            | 0         | Battery voltage       |

| 49         | CG             | _         | Chassis ground        |

| Pin<br>No. | Signal<br>Name | Direction | Definition                      |

|------------|----------------|-----------|---------------------------------|

| 2          | AB11           | 0         | Address bus 11                  |

| 4          | AB13           | 0         | Address bus 13                  |

| 6          | AB 2           | 0         | Address bus 2                   |

| 8          | AB O           | 0         | Address bus 0                   |

| 10         | AB 3           | 0         | Address bus 3                   |

| 12         | AB 5           | ٥         | Address bus 5                   |

| 14         | AB 7           | 0         | Address bus 7                   |

| 16         | AB 9           | O         | Address bus 9                   |

| 18         | DB 1           | 1/0       | Data bus 1                      |

| 20         | DB 3           | 1/0       | Data bus 3                      |

| 22         | DB 5           | 1/0       | Data bus 5                      |

| 24         | DB 7           | 1/0       | Data bus 7                      |

| 26         | BUAK           | 0         | Bus acknowledge                 |

| 28         | WAIT           | I         | Wait                            |

| 30         | HLTA           | 0         | Halt acknowledge                |

| 32         | GND            | _         | Signal ground                   |

| 34         | SPI            |           | Speaker                         |

| 36         | MRQ            | 0         | Memory request                  |

| 38         | CLK            | 0         | 2.45 MHz                        |

| 40         | IORQ           | 0         | I/O request                     |

| 42         | DW             | 0         | Data write                      |

| 44         | OFF            | 0         | Initializilng signal of IC "6A" |

| 46         | TXD            | 0         | Senal send data                 |

| 48         | BK2            | þ         | Bank exchange                   |

| 50         | CG             |           | Chassis ground                  |

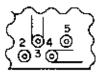

Table 1-14 CN9 (Bar Code Read Interface) Pin Assignments

| Pin No. | Signal name | Definition           |

|---------|-------------|----------------------|

| 1       | G           | Signal ground        |

| 2       | +5          | Circuit voltage      |

| 3       | ваот        | Bar code reader data |

Table 1-15 CN10 (Analog Input Interface) Pin Assignments

| Pin No. | Signal name | Definition           |

|---------|-------------|----------------------|

| 1       | G           | Signal ground        |

| 2       | ANIN        | Analog input         |

| 3       | TRIG        | Analog trigger input |

Table 1-16 CN11 (External Speaker Interface) Pin Assignments

| Pin No. | Signal name | Definition     |

|---------|-------------|----------------|

| 1       | EXSPG       | Speaker ground |

| 2       | EXSP        | Speaker signal |

# 1.5 Connection Cable (option)

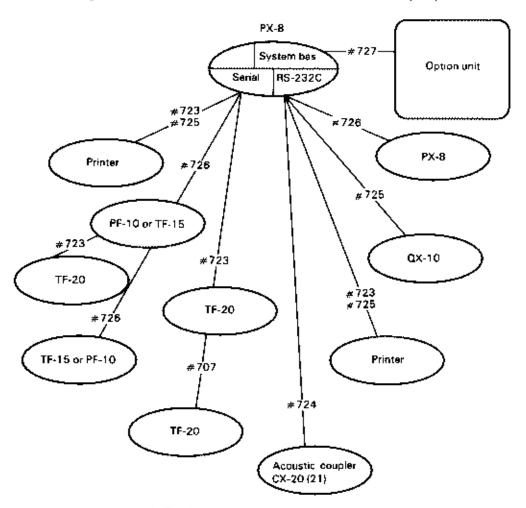

Fig. 1-8 shows in a diagram the information cables for all the available peripheral devices.

Fig. 1-8 Peripheral Device Information Cables

Table 1-17 Information Cables Specific to the PX-8 Computer

| No.         | Interface                 | Part No.                     |

|-------------|---------------------------|------------------------------|

| <b>#723</b> | High speed serial         | Y204080000 (Y204080400JAPAN) |

| #724        | RS-232C                   | Y204080100 (Y204080500JAPAN) |

| #725        | RS-232C                   | Y204080200 (Y204080600JAPAN) |

| #726        | High speed serial/RS-232C | Y204080300 (Y204080700JAPAN) |

| <b>#727</b> | Expansion interface       | Y204301000                   |

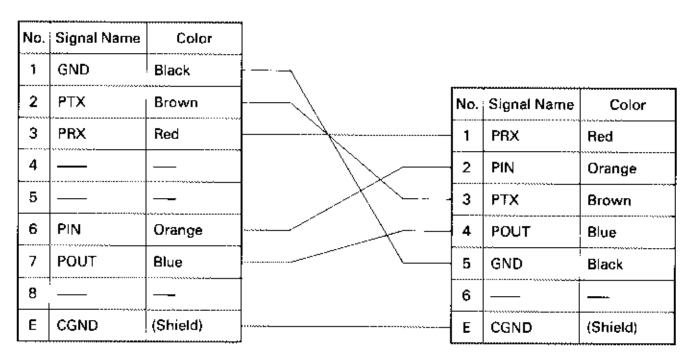

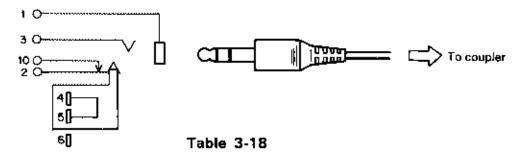

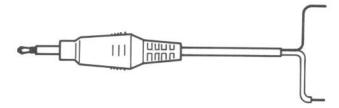

(1) #723 cable

Usage : Connection to dedicated floppy disk drive

Connector: Round-type miniature, DIN6

Fig. 1-9

#723, simple serial cable, consists of two lines: the send/receive data line and the I/O control line. Therefore, devices which can be connected via this cable are intelligent terminals only (that is, dedicated floppy disk drives) that can be controlled by PIN, POUT.

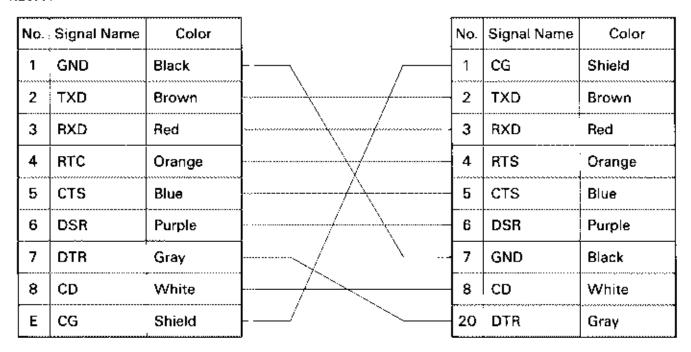

#### (2) #724 cable

Usage : Connection to acoustic coupler Connector: Round-type miniature, DB25

Fig. 1-10

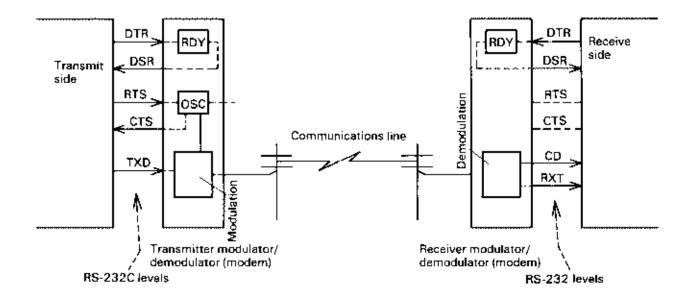

This MODEM connector cable conveys RS-232C interface signals.

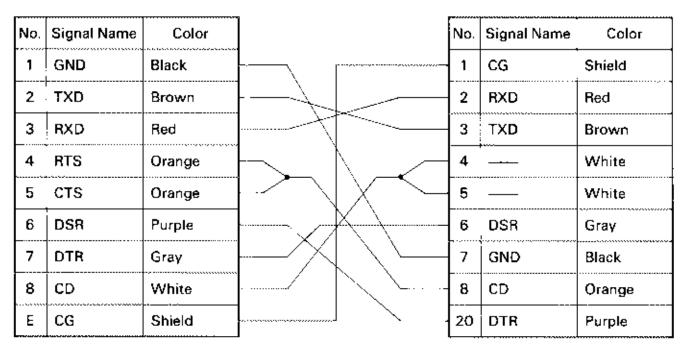

#### (3) #725 cable

Usage : Connection to printer with RS-232C interface

Connector: Round-type miniature, DB25

Fig. 1-11

#### (4) #726 cable

Usage : Connection between two units or more

Connector: Round-type miniature Round-type miniature

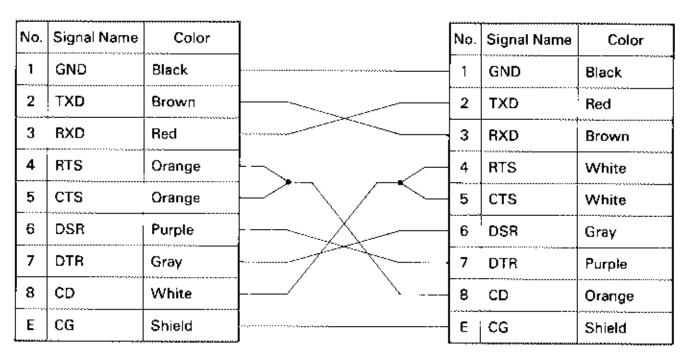

Fig. 1-12

An shown in Fig. 1-11, control lines of DSR and DTR, and connected lines of CTS and RTS (connected to CD) are crossing respectively. Therefore, when transmitting data or receiving, both units must open RS-232C interfaces.

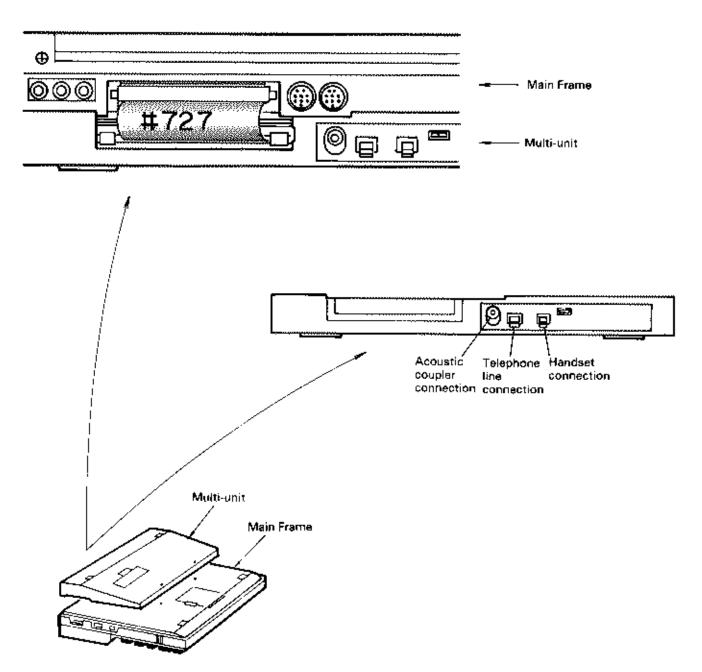

#### (5) #727 cable

Usage : 0

: Connection to optional unit

Connector: ERC-AA50 - 30 (S)

See Page 1-13 CN8 for signals.

# CHAPTER 2 PRINCIPLES OF OPERATIONS

| 2.1  | General                   | 2-1   |

|------|---------------------------|-------|

| 2.2  | Power Supplies            | 2-4   |

| 2.3  | CPU Operations            |       |

| 2.4  | Clock Generator Circuit   |       |

| 2.5  | Jumper and Switch Setting |       |

| 2.6  | Reset                     |       |

| 2.7  | Keyboard                  | 2-64  |

| 2.8  | LCD Unit                  | 2-73  |

|      | A-D Converter             |       |

| 2.10 | ROM Capsule               | 2-96  |

| 2.11 | RS-232C Interface         | 2-100 |

| 2.12 | Serial Interface          | 2-108 |

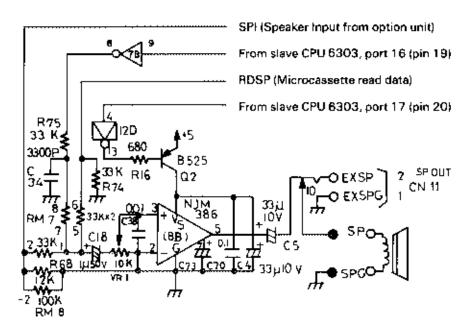

| 2.13 | Speaker Circuit           | 2-111 |

| 2.14 | Dynamic RAM               | 2-114 |

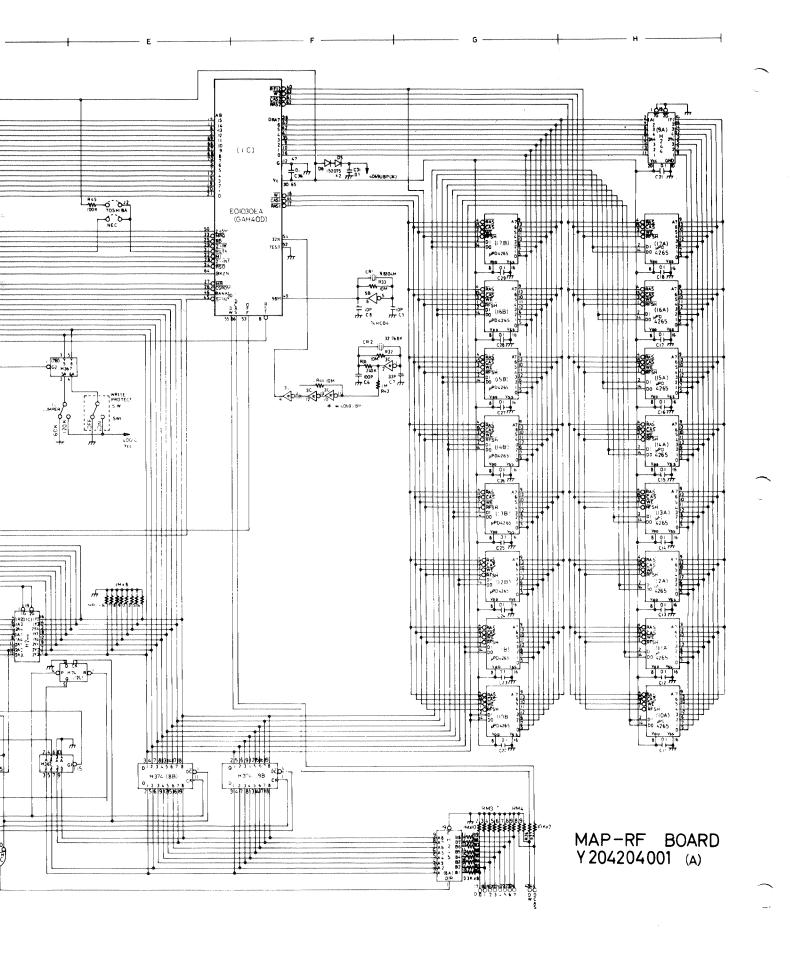

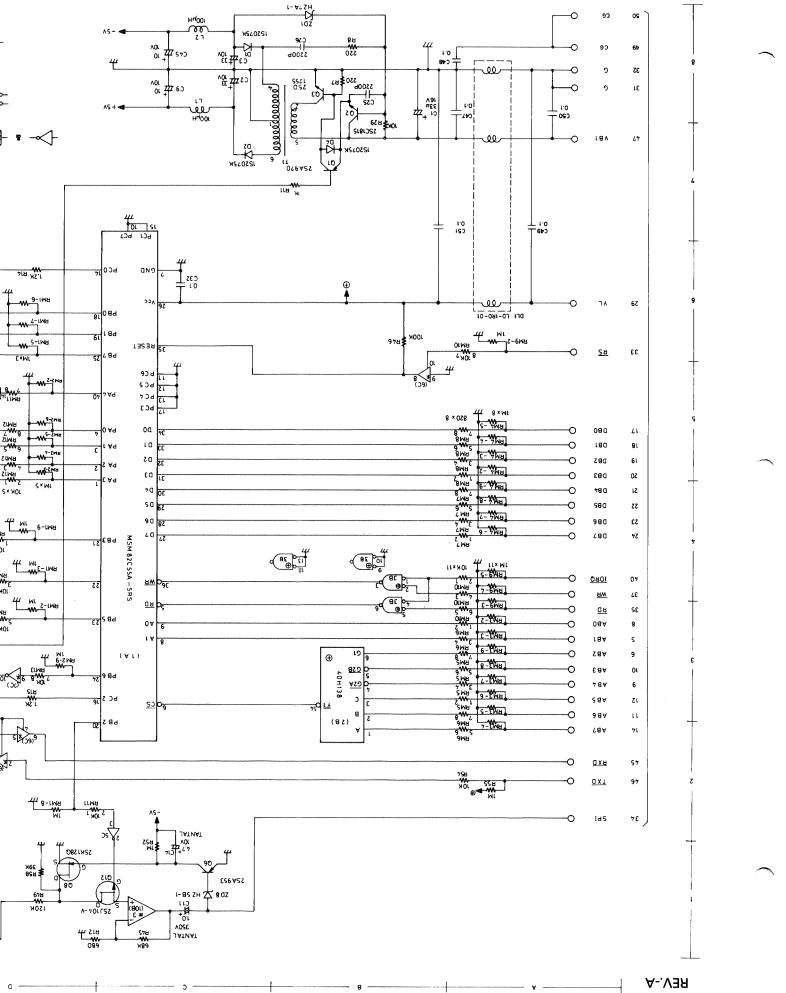

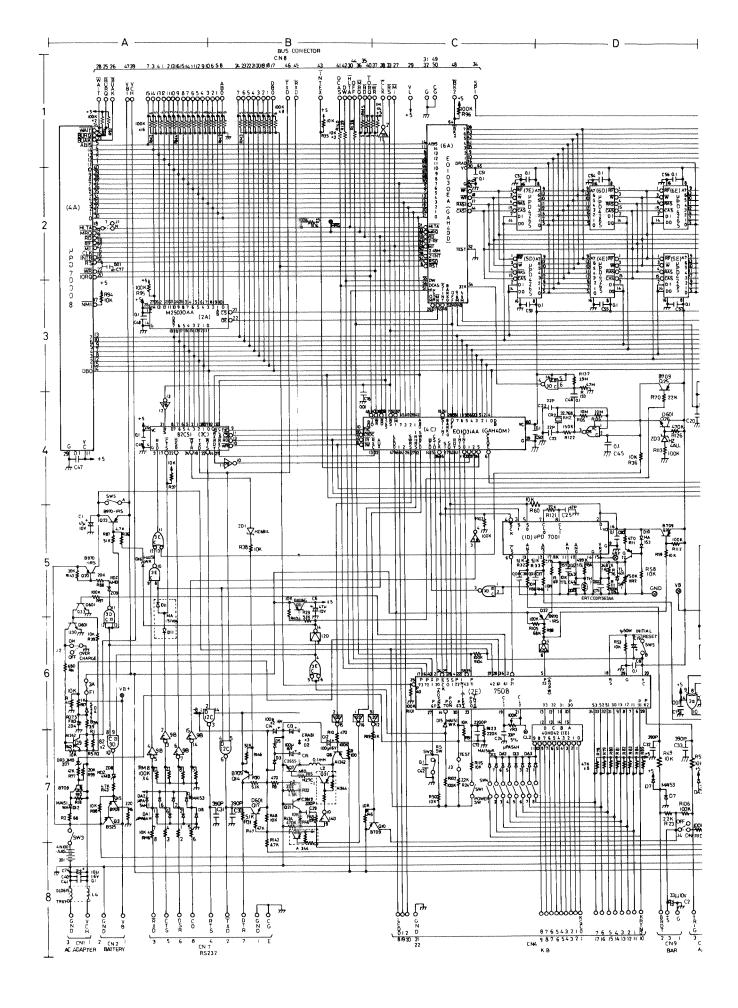

#### 2.1 General

This chapter describes various functions of the main control board (called MAPLE board) which is the center of this computer. The microcassette drive and option units are described in Chapter 3. The MAPLE board uses a diversity of fully customized ICs (referred to as gate arrays throughout this manual), masked ROMs, and other chip elements (resistor, capacitor, transistor, and diode chips) which simplify component mounting. As many CMOS elements as possible have been used in order to lower power consumption. In addition, the computer provides the following features in order to control functions specific to battery powering:

(1) Battery backup:

Protects data in RAM,

(2) Battery distribution (main and auxiliary battery power supplies):

Ensures a more reliable battery backup.

(3) Charge control:

Prevents excess Ni-Cd battery charging.

(4) Power distribution:

Outputs the supply voltages only while the computer is in operation in order to minimize battery consumption.

(5) Low voltage detection:

Automatically changes the main battery to the auxiliary battery supply.

In addition, the computer is provided with a software automatic power-off feature which prevents the battery from being discharged out if the computer is inadvertently left on.

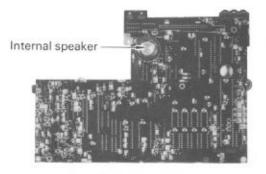

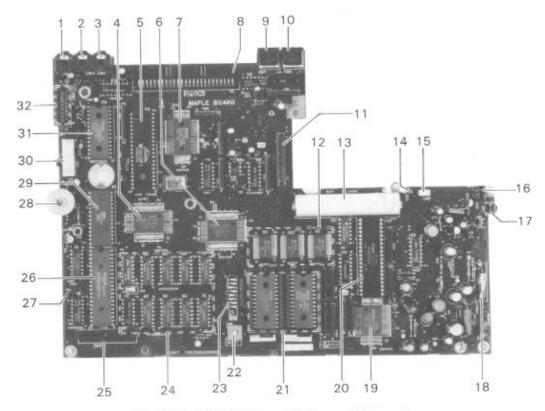

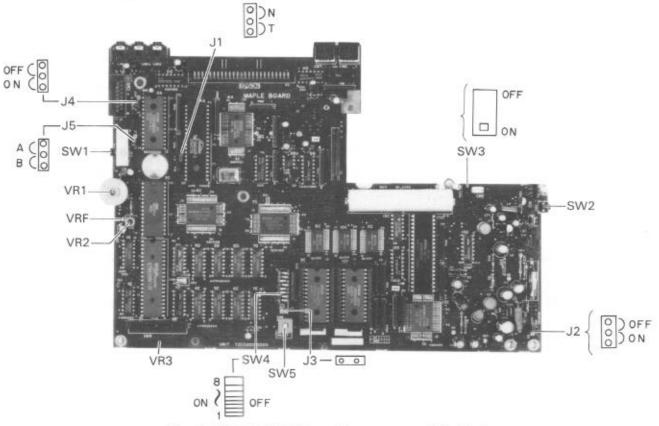

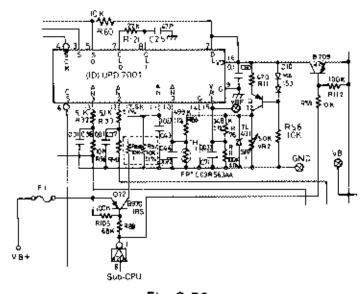

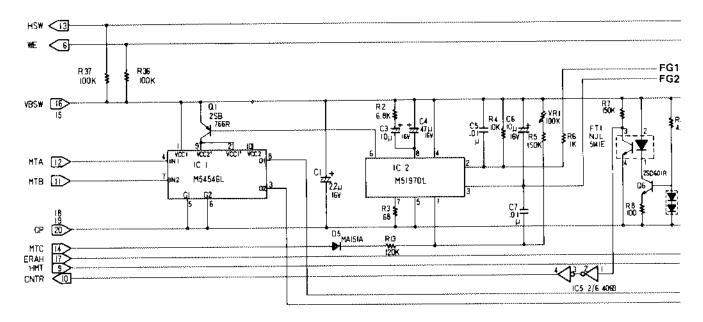

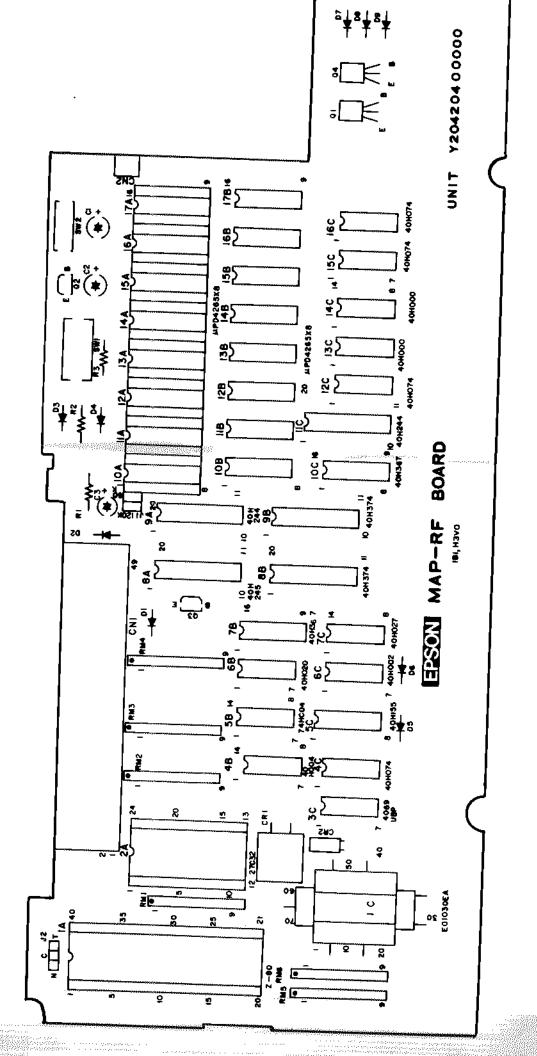

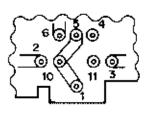

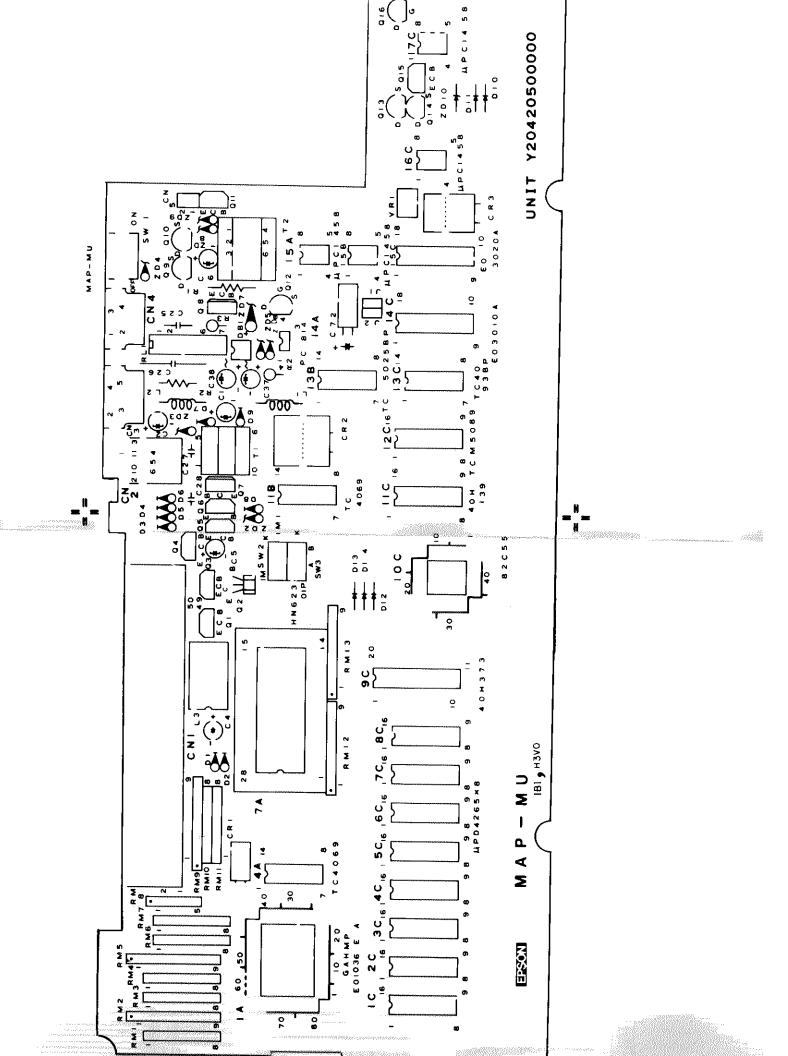

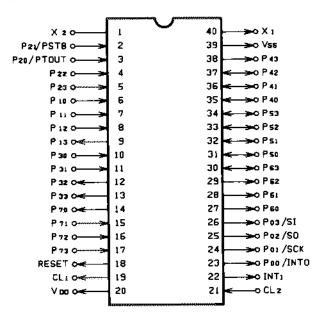

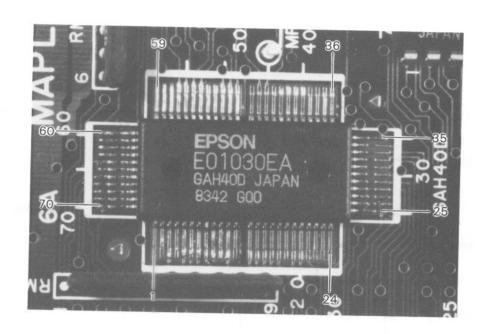

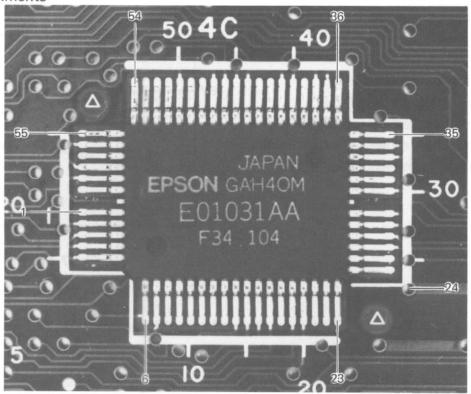

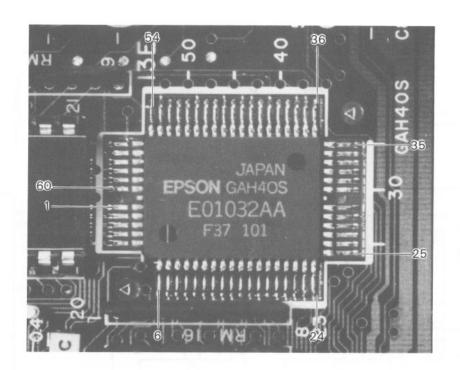

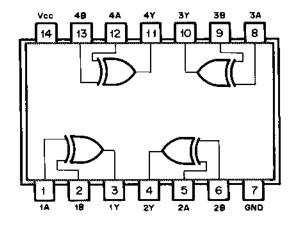

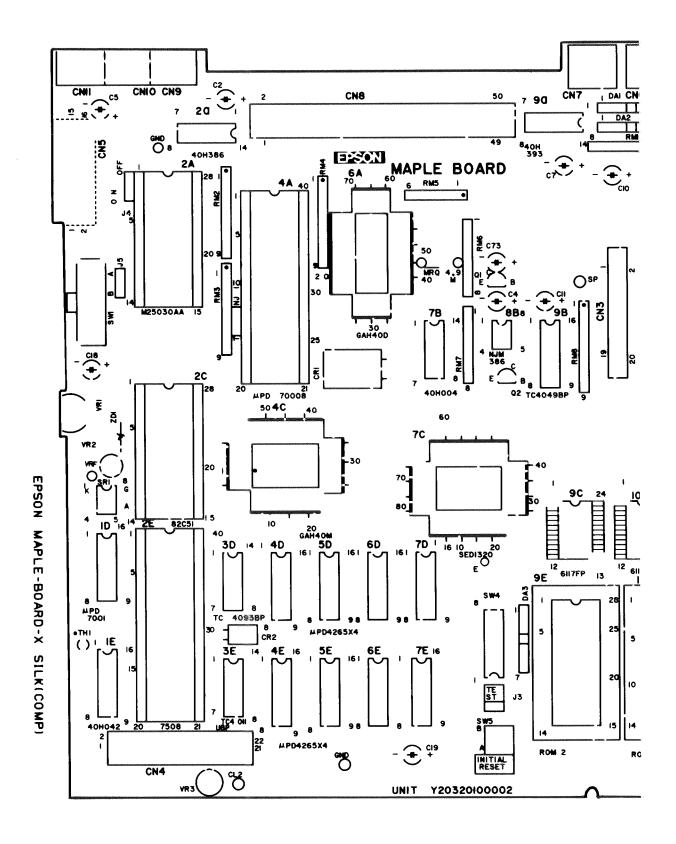

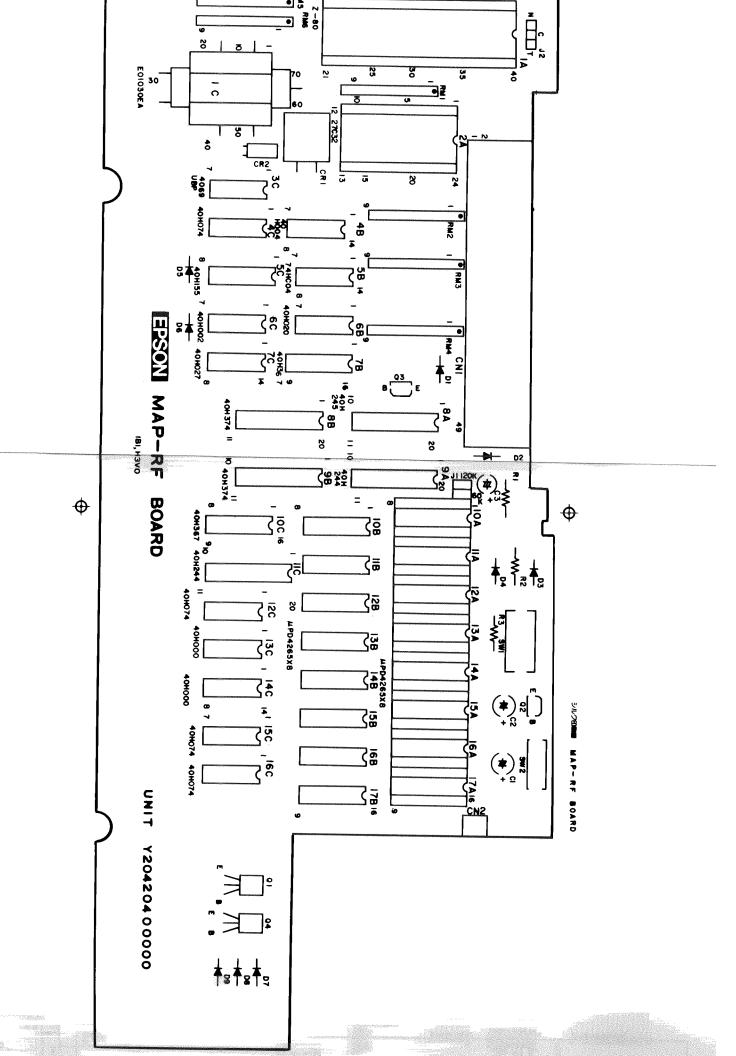

#### 2.1.1 Major Components

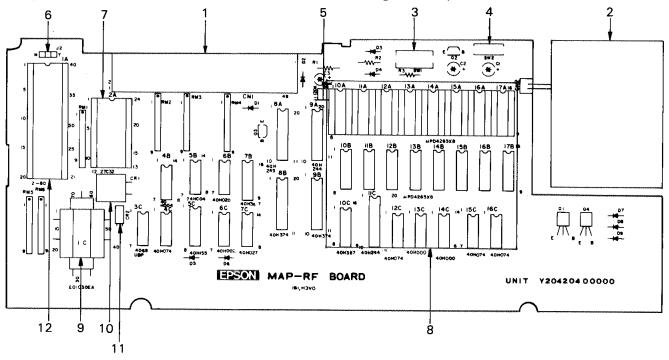

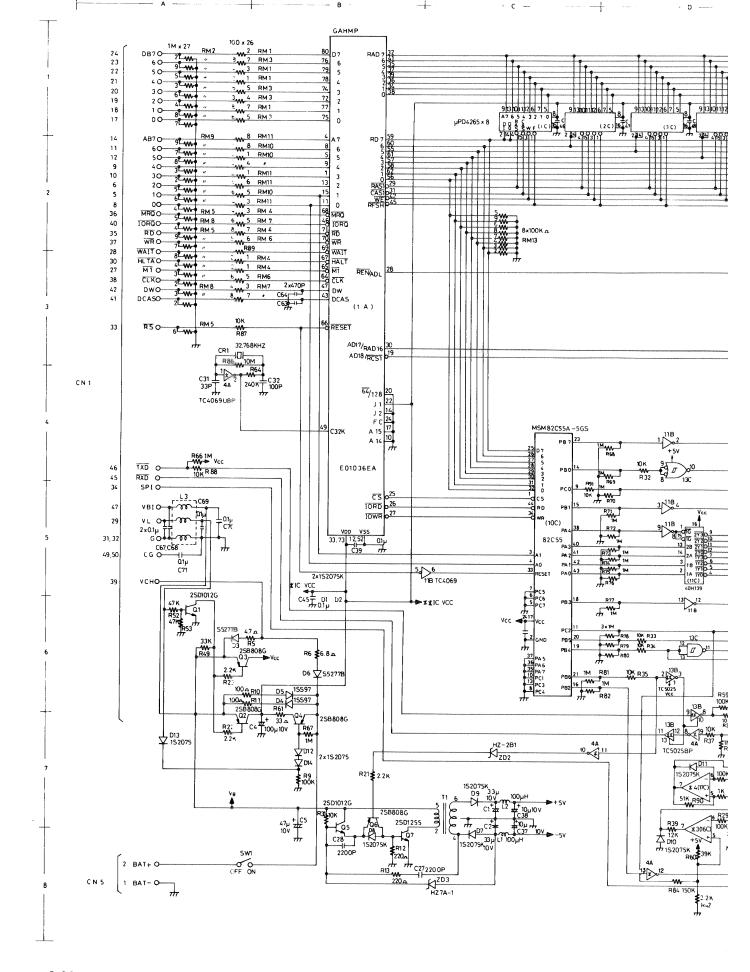

The MAPLE board has elements mounted on both the sides. A speaker and elements such as resistor packages, etc. are mounted on one side, while elements such as connectors, switches, and LSI chips, etc. are mounted on the opposite side as shown in Fig. 2-1. Table 2-1 lists major board elements together with a summary of their function.

Fig. 2-1 MAPLE Board Element Layout

Table 2-1 MAPLE Board Major Components

| No.          | Name              | Function                               |  |

|--------------|-------------------|----------------------------------------|--|

| 1            | CN11              | External speaker connector             |  |

| 3 CN9        |                   | Barcode reader connector               |  |

| 5 Main CPU   |                   | Z80 CPU package                        |  |

| 7 Gate array |                   | GAH40D package                         |  |

| 9            | CN7               | RS-232C interface connector            |  |

| 11           | CN3               | Microcassette interface con-<br>nector |  |

| 13           | Auxiliary battery | 90 mAH backup battery                  |  |

| 15           | CN2               | Main battery connector                 |  |

| 17           | SW2               | Reset switch                           |  |

| 19           | Gate array        | GAH40S package                         |  |

| 21           | ROM capsule       | (32 kB × 2)                            |  |

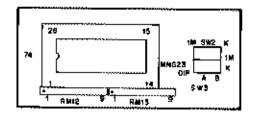

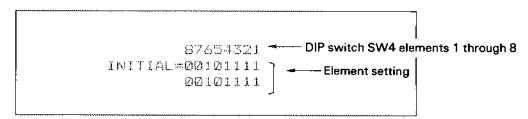

| 23           | SW4               | 8-position DIP switch                  |  |

| 25           | CN4               | Keyboard interface connector           |  |

| 27           | TH1               | Thermistor (for temperature sensing)   |  |

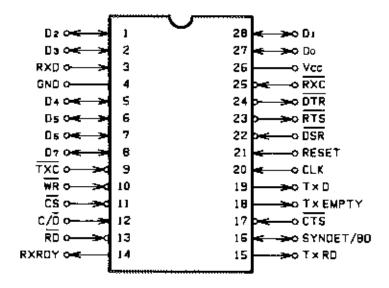

| 29           | Serial controller | 82C51 package                          |  |

| 31           | ROM               | 32kB ROM                               |  |

| No.              | Name       | Function                                                    |  |

|------------------|------------|-------------------------------------------------------------|--|

| 2                | CN10       | Analog signal input conne-<br>ctor                          |  |

| 4                | Gate array | GAH40M package                                              |  |

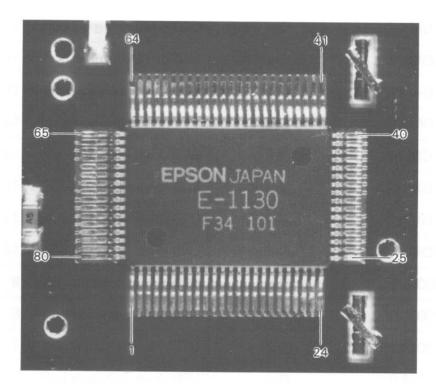

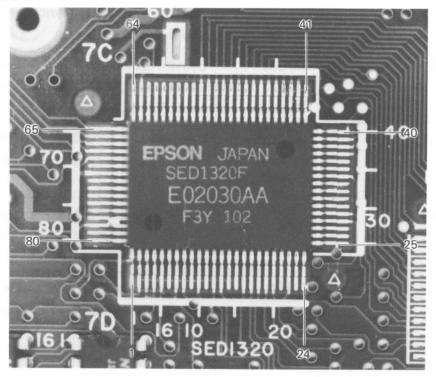

| 6 LCD controller |            | SED 1320 package                                            |  |

| 8 CN8            |            | Expansion interface connector                               |  |

| 10 CN6           |            | Serial interface connector                                  |  |

| 12               | V-RAM      | 6kB LCD RAM                                                 |  |

| 14               | SW3        | Auxiliary battery control switch                            |  |

| 16               | CN1        | AC adaptor input (charge in-<br>put) connector              |  |

| 18               | F1         | Fuse 3A                                                     |  |

| 20               | Sub-CPU    | 6303 CPU package                                            |  |

| 22               | SW5        | Initial reset switch                                        |  |

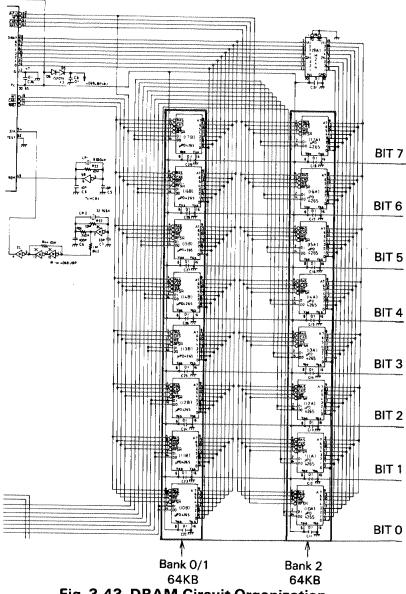

| 24               | D-RAM      | 64kB×8                                                      |  |

| 26               | 4-bit CPU  | 7508 CPU package                                            |  |

| 28               | VR1        | Speaker volume visual angle<br>adjustment variable resistor |  |

| 30               | SW1        | Power switch                                                |  |

| 32               | CN5        | LCD interface                                               |  |

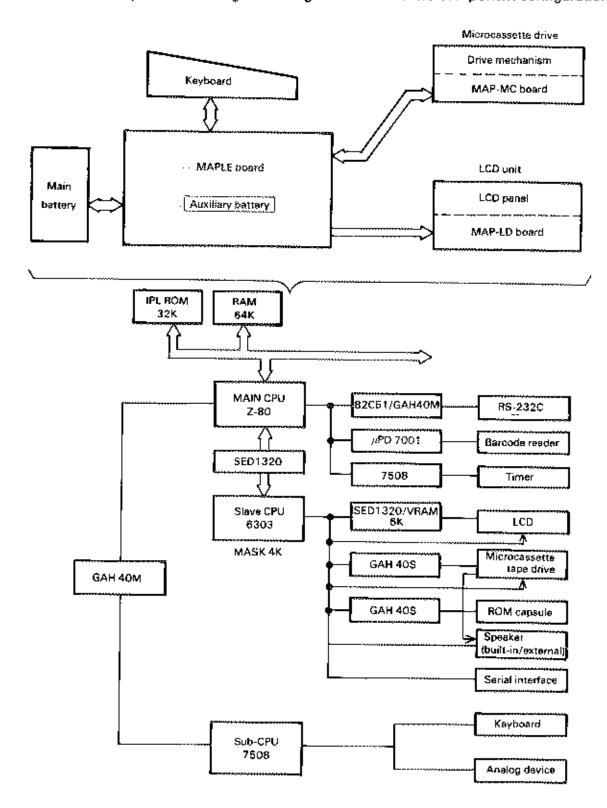

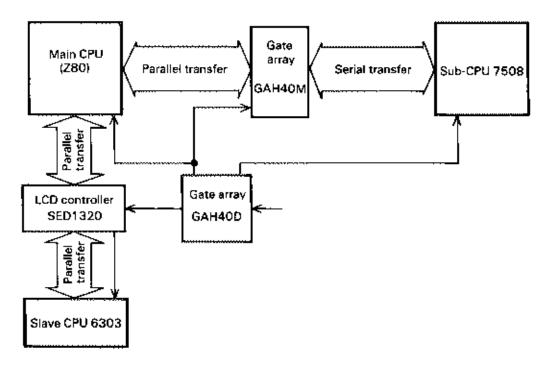

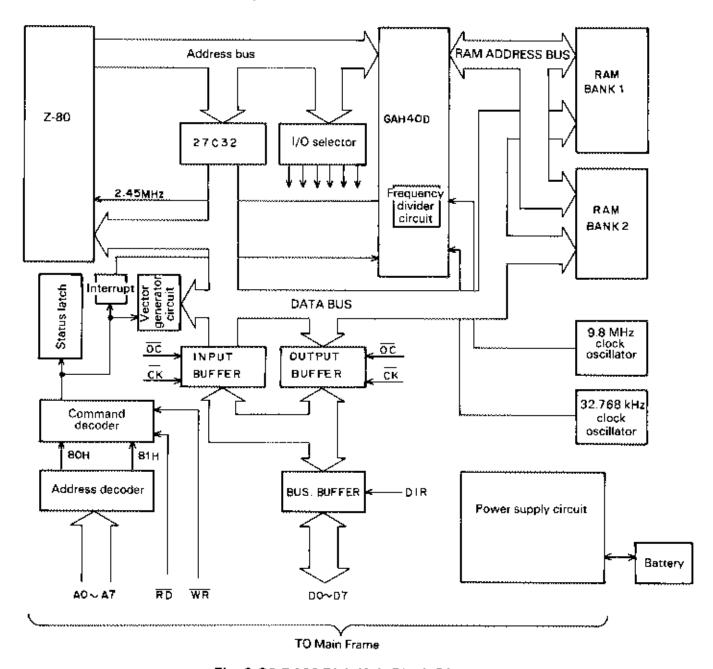

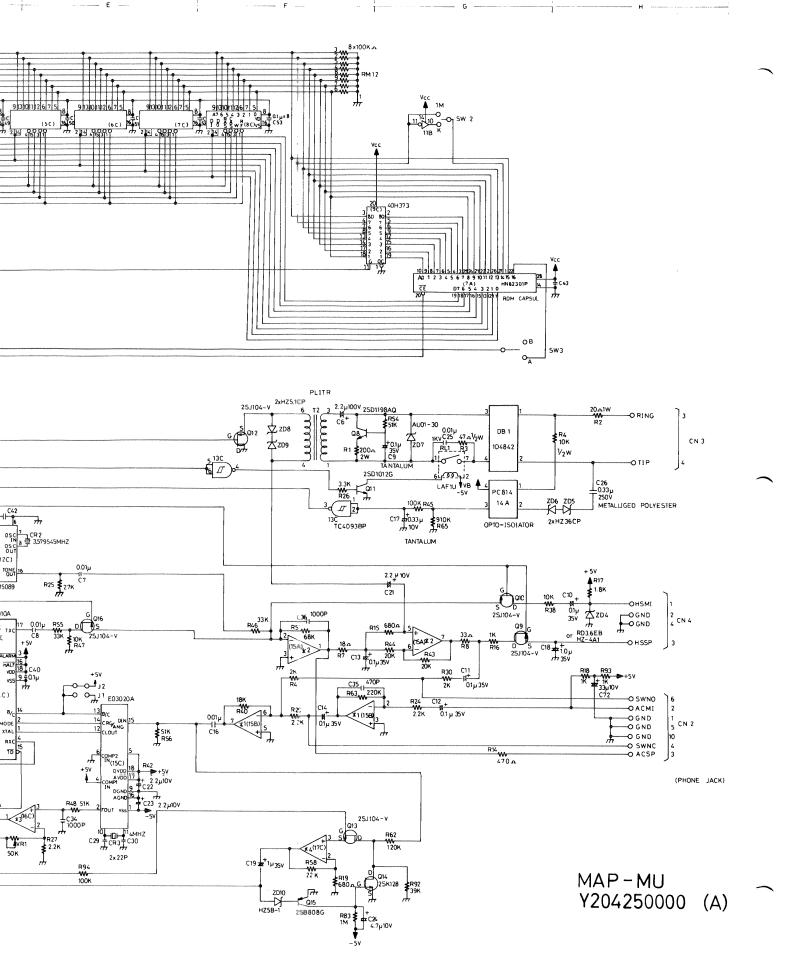

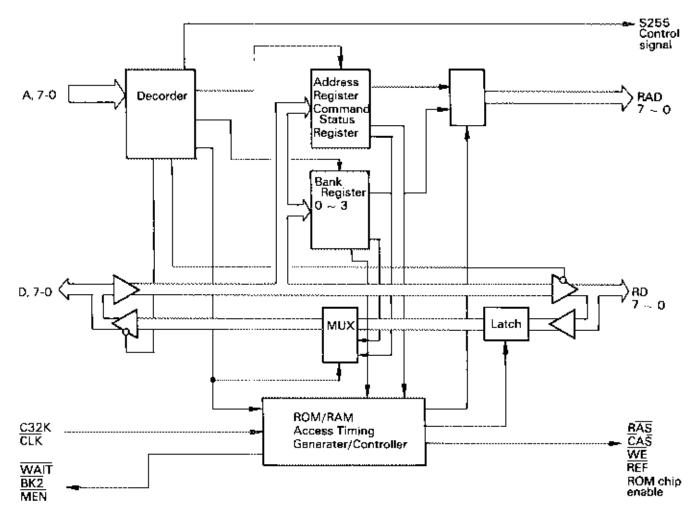

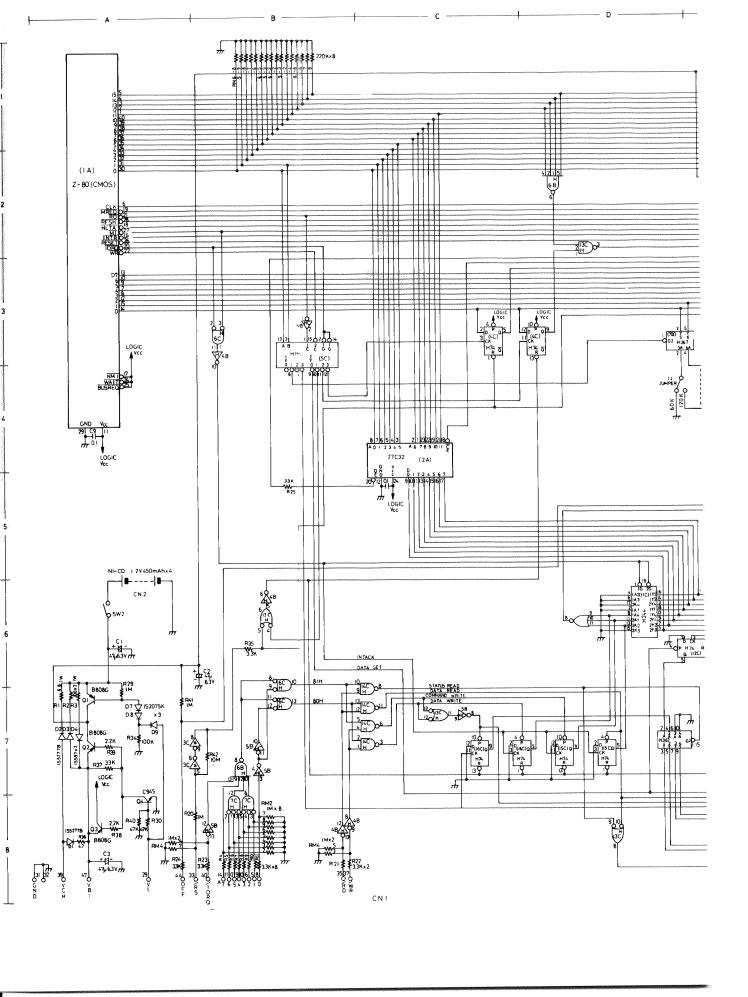

#### 2.1.2 System Configuration

PX-8's main components include a main battery; the MAPLE (main) board, which along with control circuitry also contains an auxiliary battery; the LCD unit; the keyboard; and the microcassette drive assembly. The following block diagram demonstrates component configuration.

Fig. 2-2 Computer Configuration

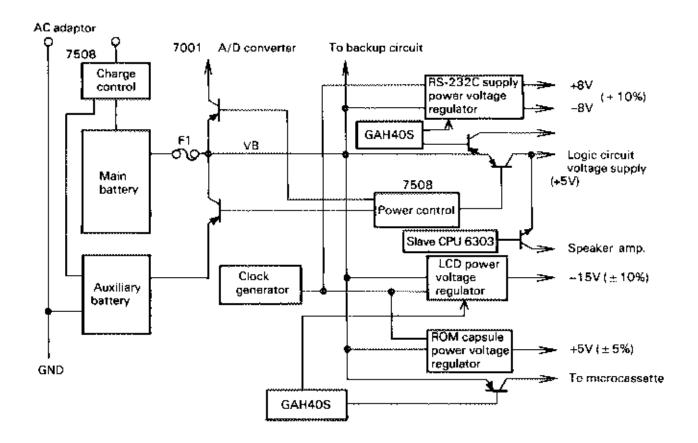

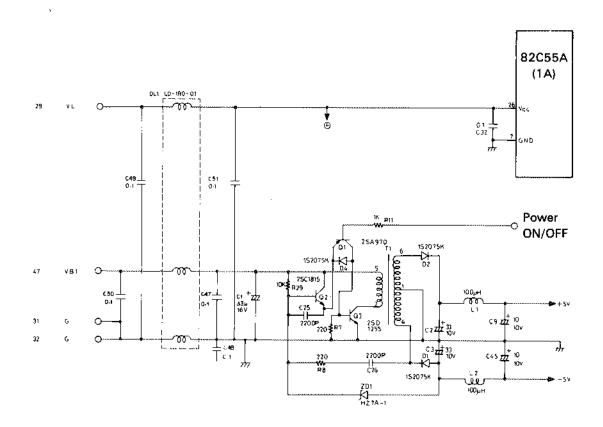

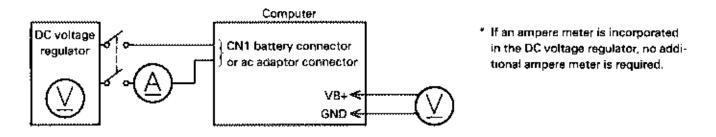

## 2.2 Power Supply

This computer operates with a rechargeable Ni-Cd battery and is provided with features for minimizing power consumption and controlling battery charge. The power supply is summarized in the following:

Batteries: Two batteries; main and auxiliary, are used.

Auxiliary battery ............... Also supplies the DC 4.8V power. It has a capacity of 90 mAH and backs up the main battery when in a low voltage (discharged) condition.

- Charging circuit: Supplies charging current to the main and auxiliary battery when an AC adaptor is connected. This circuit, which operates in either of two modes; normal and tricle (low current) charges, under the control of a sub-CPU 7508, controls the charging current.

- Voltage detection circuit: Monitors the voltage of the main battery using an internal AD converter. The result is processed by the sub-CPU 7508 to cause the circuit to provide two functions. One is low voltage detection which allows the computer, if it is operating, to display a warning message "CHARGE BATTERY" on the LCD screen, when the battery power (i.e., voltage) falls below a certain level. In addition, this function causes the computer to stop at an appropriate point in the operation in progress. The other function determines the normal charge restart timing; causing a switch from tricle to normal charge when AC adapter is connected.

- Backup circuit: Supplies the power required to maintain data in the RAMs when the power switch is off or the computer is not connected to the AC power line. It also serves to normally operate the circuits which monitor the battery voltage and detect whether power is on.

- ±8V regulator: This voltage regulator supplies DC voltages of +8V required for RS-232C operations. The voltages are generated from the battery voltage (VB) only when the RS-232C or serial interface is used.

- -15V regulator: Supplies a -15V DC voltage used for LCD display control. This voltage is generated from the battery voltage (VB) as long as power is on.

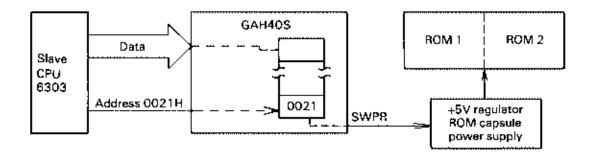

- 5V regulator: Supplies a +5V DC voltage used for the PROM capsule. This voltage is generated from the battery voltage (VB) only when the PROM is accessed. The regulator is provided in order to prevent a transient due to PROM access from directly affecting the VB line.

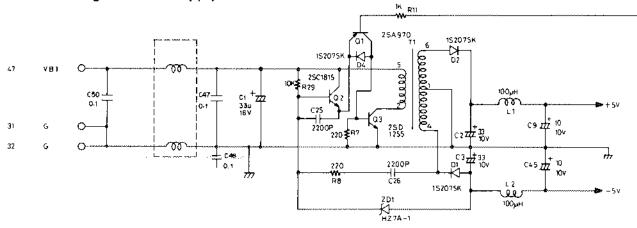

Other power circuits such as a switching circuit, which supplies the logic circuit power, are located on the MAPLE board, in addition to the above. Fig. 2-3 is a block diagram which summarizes the power supply circuits on the MAPLE board.

Fig. 2-3 Power Circuit Block Diagram

#### 2.2.1 Power On/Off Control

The power circuits are controlled by the 4-bit CPU 7508 which operates under a control program stored in a mask ROM built in it. If the CPU runs away due to some reason (battery power exhaustion for example), therefore, the power supplies are completely out of control. If this occurs, the AC adaptor should be connected to charge the batteries and then SW5 should be pressed to reset the CPU 7508.

#### 2.2.1.1 Power On

The computer is turned on by either of the following:

(1) Setting the POWER switch ON

Setting the POWER switch ON causes pin 23 of CPU 7508 (INTO) to go high (see Fig. 2-4) which interrupts the control program for turning power on.

(2) Programmed power on

Power is automatically turned on regardless of the POWER switch setting when the time specified softwarewise with a "WAKE" command coincides with that of the clock built in CPU 7508.

#### 2.2.1.2 Power Off

Power is turned off by one of the following:

(1) POWER switch OFF

Turning the POWER switch OFF causes pin 23 of the 7508 CPU (INTO) to go low (see Fig. 2-4), interrupting the control program for turning power off.

(2) Low voltage detection

When a low VB line voltage is detected. The 7508 CPU interrupts the main CPU and current processing to be terminated at an appropriate point. At the same time, "CHARGE BATTERY" message display on the LCD screen for 30 seconds. The 7508 CPU then automatically turns power off if the POWER switch is at the ON position.

(3) Automatic (programmed) power off

The computer can be turned off by a software automatic power-off feature which uses the 7508 CPU's built in clock. This feature automatically turns power off when no I/O unit is used for a certain period of time even though the computer is in the key entry mode. Power off timing as follows:

Default: 10 minutes

Specified: 1 to 255 minutes (specified by using the CONFIG command)

The following is a circuit diagram including the power on/off circuit:

Fig. 2-4 Power On/Off Control Circuit

- \* The power-off operation involves the following component functions:

- Microcasette tape drive head unloading

- Microcassette tape drive power off

- P-ROM cartridge power off

- RS-232C power off

- Barcode reader power off

- Speaker power off

It also controls the emergency power supply which allows the computer operation sequence in process to be completed and status information to be stored whenever the regular power supply is depleted.

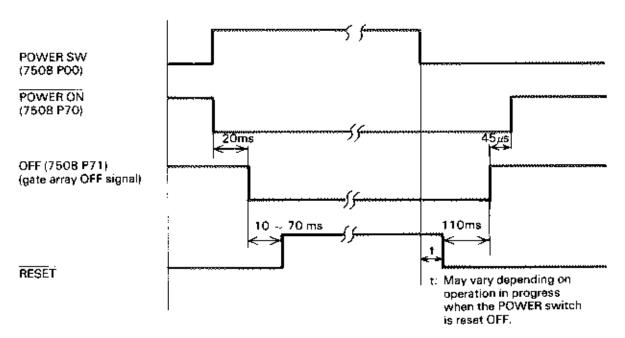

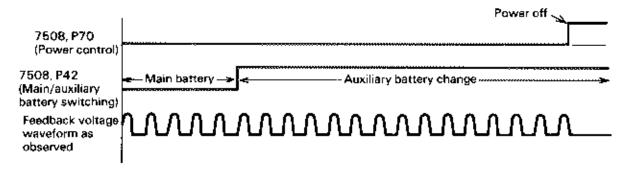

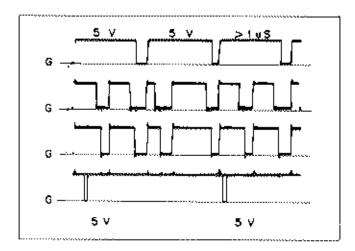

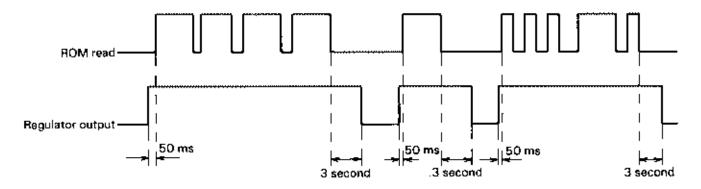

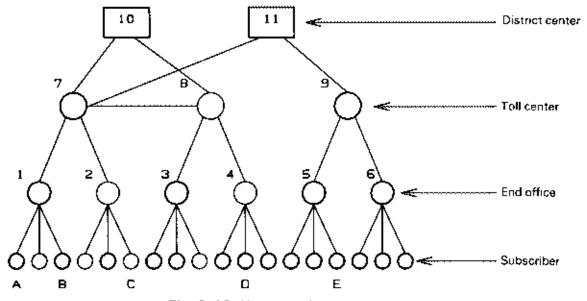

#### 2.2.1.3 Power On/Off Timing

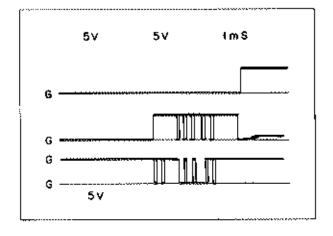

Power on/off has to be controlled by interrupting the sub-CPU 7508. Thus, either timing (the POWER ON or RESET signal) will be a little delayed as shown in Fig. 2-5

Fig. 2-5 Power On/Off Control Circuit

The time delay sequence illustrated in Fig. 2-5 above is only a sample time sequence. The power on/off operation permits any operation sequence in process, including the mechanical operation of an I/O unit (e.g., the microcassette) currently in progress, to be completed and the printer to be reinitialized before the power is off. The length of the illustrated time delay will vary according to which mechanical and/or logic sequence must be completed. The off signal is used to prevent a latch within the gate array.

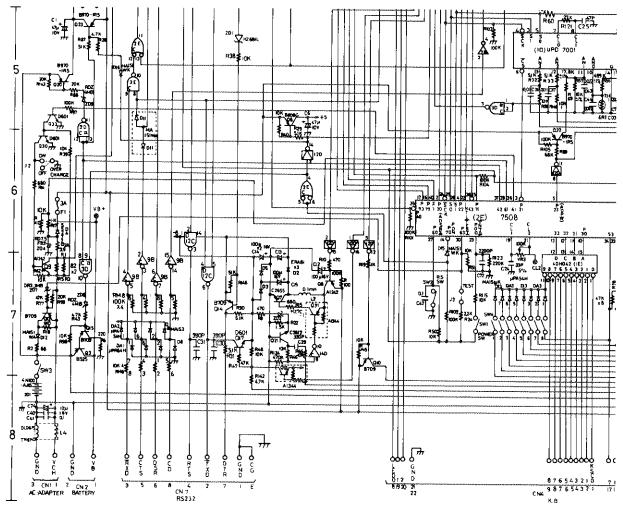

#### 2.2.1.4 Power On/Off Circuit Operations

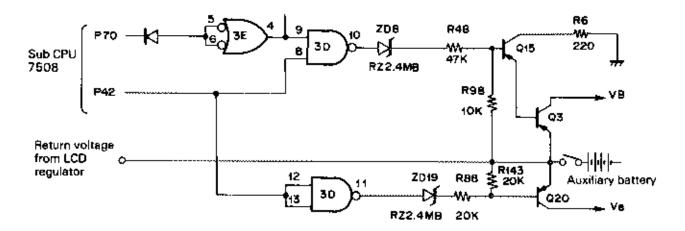

Fig. 2-6 shows the circuit. When the POWER switch is set ON or RESET off, or an automatic power on or off is input via software, the sub-CPU control program processes the power on or off as an interrupt using port 70 as follows:

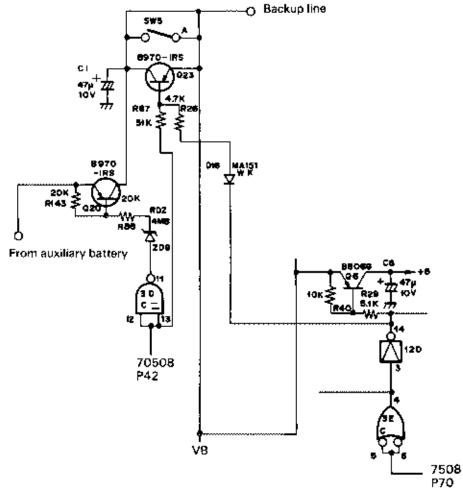

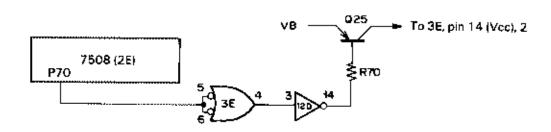

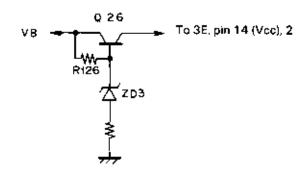

• Power on: P70 of the sub-CPU 7508 going low causes the anode of D15 to go low, turning pin 4 of IC '3E' high. This in turn causes the output at pin 14 of the next inverter, 12D, to go low. This signal is fed to transistors Q6 and Q23 through resistors R29 and D16 respectively, turning them on. This causes the VB (+) voltage to be output at the collector of Q6, supplying the operation voltage (logic circuit voltage: VL) to the elements on the board. The transistor Q23 also supplies the VB(+) voltage to the battery-backed-up elements on the board. Thus, the board is ready to operate. Port 42 of the 7508 sub-CPU controls the backup for the auxiliary battery and can enable or disable conduction through transistor Q20. When port 42 output is high, the low level at pin 11 of IC 3D breaks down zener diode ZD9, holding Q20 in conduction. In this way the LCD drive voltage is insured, the message, "CHARGE BATTERY", will be displayed whenever the main battery output voltage falls to or below the low voltage limit.

Fig. 2-6

#### Note:

P70: POWER ON signal

High turns power off, and

Low turns power on.

P42: Main → auxiliary battery switching signal

High selects auxiliary battery, and

Low select main battery.

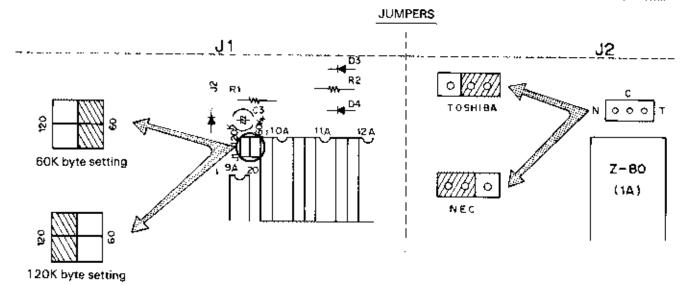

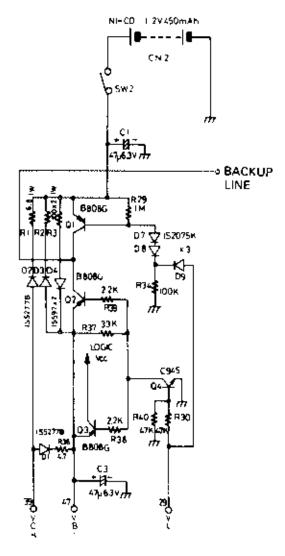

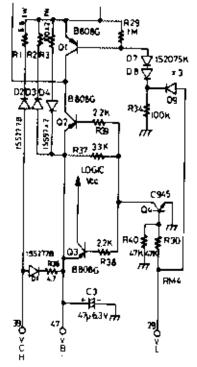

#### 2.2.2 Charging Circuit

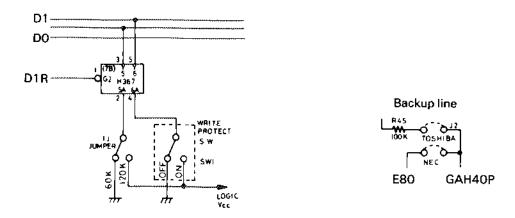

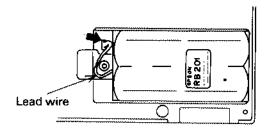

Two 4.8V, rechargeable, Ni-Cd batteries are connected to the MAPLE board. The main battery, which is housed the bottom case and can be replaced by loosening a single screw, has the larger capacity of 1100 mAH. Its charging circuit includes an overcharge protection circuit which protects the battery from overcharge by automatically discontinuing charge. The auxiliary battery, which is mounted on the MAPLE board, has a capacity of 90 mAH. A switch is inserted in both the charging circuit and backup line which can disable the backup by the auxiliary battery.

#### 2.2.2.1 Main Battery Charging Circuit

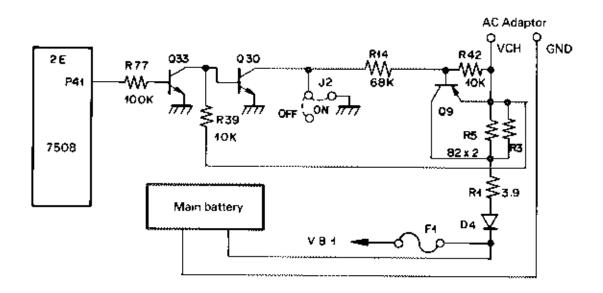

Fig. 2-7 Main Battery Charging Circuit

The charging circuit includes jumper A2 which allows two modes of charging:

When J2 is jumpered...... No Overcharge Protection Control

Jumpering J2 causes the base of transistor Q9 to be always tied to ground, holding it in conduction. This effectively bypasses resistors R3 and R5, inserted in the charging circuit in series, and causes the charging current to be supplied to the battery through transistor Q9, current limiting resistor R1, and reverse-current preventing diode D4. This setting ecuses the battery to be continually charged as long as the AC adaptor is connected. Because of the low current limiting resistance in the mode of operation, the battery is highly liable to overcharge.

When J2 is open ...... Shipment Setting

• When J2 is open, the charge current bypassing transistor Q9 is controlled by the port 41 output of the 4-bit sub-CPU 7508. This CPU has a clock feature built in and maintains port 41 at the low level only for the <u>first eight hours</u> after it detects that the AC adaptor is connected, providing the same charging mode as when the jumper J2 is closed. With port 41 held low, transistor Q33 is cut off, leaving its collector at the high level (The collector is pulled up to the ac adaptor output through the resistor R39.) This maintains transistor Q30 in conduction; the collector is held at the low level, providing the same effect as if jumper J2 were closed.

• When eight hours have elapsed after the ac adaptor is connected to the AC line, port 41 of the 4-bit sub-CPU goes high, cutting off transistor Q9. This puts the circuit in the trickle charging state by inserting the resistors R3 and R5 (combined resistance, 41 ohms) in the charging path in series. The circuit constants are selected in this state so that the battery is substantially not harmed by overcharge, even if the battery is continually charged.

#### \*Reference

Following is the sub-CPU port operation for power control:

Table 2-2 Sub-CPU Port Operation

| Port      | Direction | Meaning :                                          | Signal<br>level | Function                                                                                        |

|-----------|-----------|----------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|

| P00       | IN        | Power switch                                       | Low             | Power switch "OFF" interruption (H $\rightarrow$ L: $\square$ )                                 |

|           |           | interruption                                       | High            | Power switch "ON" interruption (L → H:f )                                                       |

| 200       | Out       | Main battery                                       | Low             | Inactive                                                                                        |

| P23       |           | voltage detection                                  | High            | Active Supply main battery voltage to A/D converter Supply operational voltage to A/D converter |

| P40       | out       | Reset                                              | Low             | Reset main CPU, slave CPU, etc.                                                                 |

|           |           |                                                    | High            | Inactive                                                                                        |

| P41       | Out       | Recharging mode                                    | Low             | Normal recharging mode                                                                          |

| <b>F#</b> | Out       | control                                            | High            | Trikle recharging mode                                                                          |

| P42       | Out       | Battery back-up                                    | Low             | Back-up with main battery                                                                       |

|           |           | control                                            | High            | Back-up with auxiliary battery                                                                  |

| P60       | i In      | Reset switch                                       | Low             | Active source input of "P40" and "OFF"                                                          |

|           |           |                                                    | High            | Inactive                                                                                        |

| P61       | In        | AC adapter (re-<br>charging opera-<br>tion) detect | Low             | No AC adapter (non recharging condition)                                                        |

|           |           |                                                    | High            | Recharging condition (AC adapter is plugged)                                                    |

| P63       | Out       | Recharging mode<br>for auxiliary bat-<br>tery      | Low             | Normal recharging mode                                                                          |

|           |           |                                                    | High            | Trikle recharging mode                                                                          |

| P70       | Out       | Powr ON                                            | Low             | Power ON                                                                                        |

|           |           |                                                    | High            | Power OFF                                                                                       |

| P71       | Out       | "OFF" signal for                                   | Low             | Active (Initialize the '4C' '6A')                                                               |

|           |           | gate array (6A, 4C)                                | High            | Inactive                                                                                        |

#### 2.2.2.2 Main Battery Charging

In the following text, the functions of jumper J2 are summarized. Then, the actual main battery charging operations are described based in Fig. 2-8.

#### (1) J2 jumper

The J2 jumper provides the following functions:

When closed: Disables the charging control; the battery is always charged as long as the AC

adaptor is connected.

When open: Enables the charging control; the battery is charged as follows when the AC

adaptor is connected, depending on whether power is on or off:

When power is on: The normal charge continues for the first 11 hours, and

then the trickle charge is used.

When power is off: The normal charge continues for the first eight hours, and

then the trickle charge is used.

With jumper 2 open and power off, the circuit remains in the trickle charge mode, after the normal charge, for the first eight hours. However, the circuit automatically returns to the normal charge mode whenever the battery voltage falls below 5V.

#### (2) Charging Operations

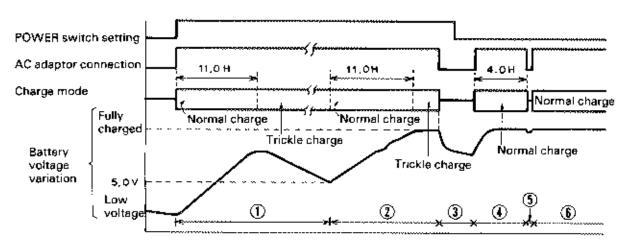

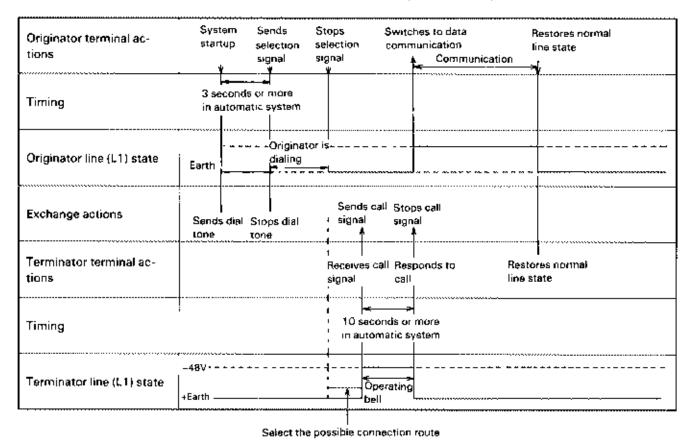

Fig. 2-8 is a timing diagram which illustrates the main battery charging operation when the charge control is in effect.

Fig. 2-8 Main Battery Charging Operation

Note: Battery voltages and charging currents:

Voltages:

When fully charged: Approx. 5.4V

Low voltage: Approx. 4.5 to 4.8V

Charging currents:

Main battery

Normal charge: 150 to 200 mA

Trickle charge: 40 mA

Auxiliary battery

Normal charge: 10 mA Trickle charge: 1 mA

- Fig. 2-8 illustrates the main battery charging operation from a low voltage. The individual steps of the operation ① through ① are explained in detail in the following:

- ① Situation Low voltage is detected while the computer is used with the AC adaptor connected.

The charging control is enable, and the battery is charged during normal computer use for aperiod of 11 hours. During that time, the battery may not be fully, charged depending on the particular use of the computer. After 11 hours, the charge mode changes to trickle charge in which the battery is charged at a current of approximately 40 mA. The figure shows a charging current of more than 40 mA, indicating that the battery is being discharged.

- ② Situation The battery voltage falls to 5.0V while the computer is used. Since the AC adaptor remains connected, the charge mode is switched back from trickle to normal charge. Sub-CPU 7508 always monitors the battery voltage using an A/D converter and, whenever it detects that the voltage has fallen to 5.0V or below, it automatically switches the mode through port 41. The circuit restores the same charging operation as ① above. The almost linear changes during the normal and trickle charges indicate that the charge and discharge currents remain almost constant during these durations.

- ③ Situation After the AC adapter is disconnected, the computer is used for a while, and then power is turned off.

While the computer is used, the battery power decreases depending on how it is used. After power off, the battery power decreases for backing up the internal circuits.

- Situation The AC adaptor is connected while the power remains off.

The eight-hour normal charge starts when the AC adaptor is connected. However, it is interrupted four hours after when the adaptor is disconnected. The battery is charged at the normal charge current during this interval regardless of the battery power.

- Situation The normal charge is interrupted by replacing the adaptor connection to another AC line outlet.

- Situation The adaptor is reconnected and the normal charge is resumed.

The eight-hour normal charge starts again when the AC adaptor is reconnected.

- Note 1: The main battery charging is controlled by detecting connection of the AC adaptor, regardless of the current residual battery power or the past charging operations. The 8- or 11-hour normal charge starts depending on whether power has been turned on or off when the adaptor is connected.

- Note 2: The battery may not be fully charged even though the adaptor is left connected for a long period of time. It is highly likely that the battery will remain below the full charge, especially when high power consuming operations are being performed while the battery charge is in process.

# When charging control is disabled

When the charging control feature is disabled, the battery is charged at the normal charge current as long as the AC adaptor is connected. Leaving the adaptor connected for a long time (overcharging the battery) may affect the life of the battery.

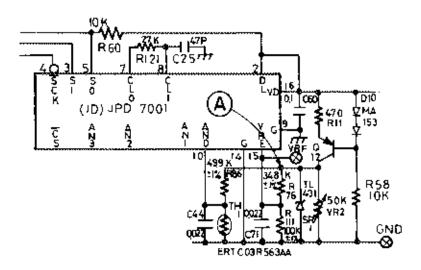

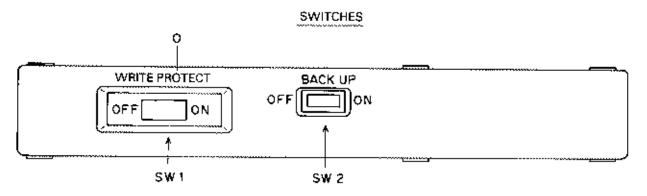

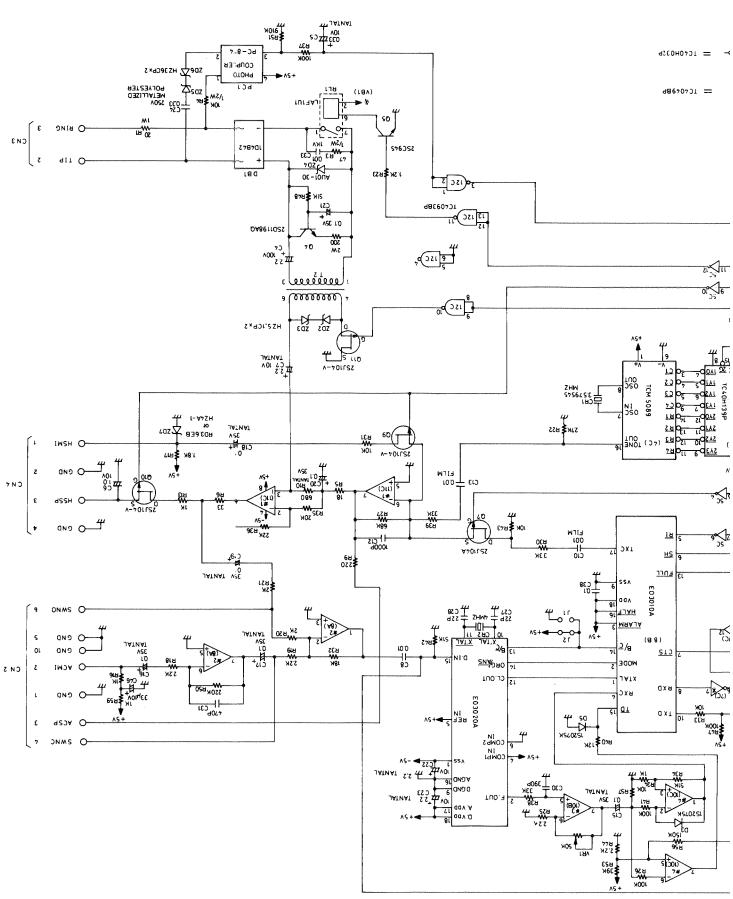

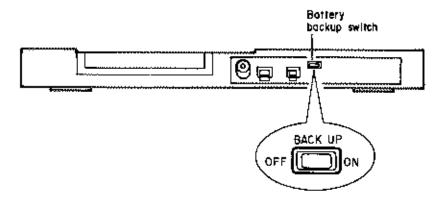

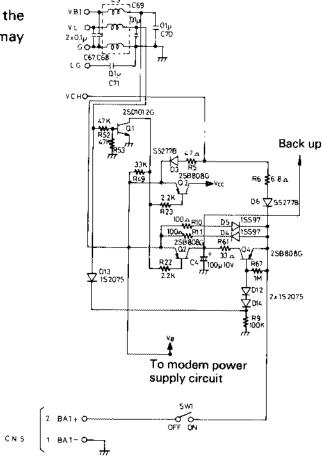

#### 2.2.2.3 Auxiliary Battery Charging Circuit

As shown in Fig. 2-9, this circuit allows the user to select, via switch SW3, whether or not to enable charging and discharging (i.e., backup by the auxiliary battery). (SW3 is normally jumpered.)

When SW3 is jumpered, the battery is charged by one of the following three modes:

- When the AC adaptor is connected:

- The auxiliary battery is charged from VCH through R18.

- (2) The auxiliary battery is charged from VCH through Q13.

- When the computer is turned on:

- (3) The auxiliary battery is charged from the LCD power supply.

- Mode (1) is a trickle (low current) charge, which is enabled when the main battery voltage is 5.0V or below.

- Mode (2) is a normal charge which is enabled after low battery voltage (VB) condition is detected. When low voltage is detected, P63 of the sub-CPU 7508 is held low for 8.0 hours, forcing the normal (high current) charge.

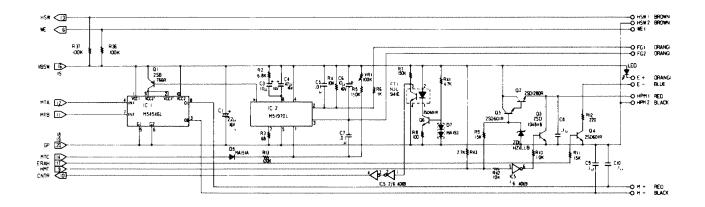

The low level at P63 causes a potential dif-

O 7505, DR3.3MB 207 20K ROZ (P70) MAISI iok ≨ 82 ₹as 8525 Auxiliary battery 9₩3 o 1800, 4N 100 -AAS 201 CD power supply. 777 167 0.1 OLO:616 Main TRBY-D battery (from AC adaptor)

Fig. 2-9 Auxiliary Battery Charging Circuit

ference of approximately 6V (VCH voltage), which is AC adapter voltage, to appear across zener diode ZD7, breaking it down (ZD7 is a 3.3V zener diode). This lowers the base voltage of transistor Q13 below the collector voltage, putting the transistor in conduction, and providing the normal charging path from the VCH line through Q13, D12, and R2.

Mode (3) constantly maintains the auxiliary battery in a fully charged state for emergency (the backup operation from the auxiliary voltage when low voltage is detected). Thus, the battery is continuously charged as long as the LCD power supply is available (whenever power is on) regardless of whether the ac adaptor is connected or not. See 2.2.5.2, LCD Voltage Regulator for details.

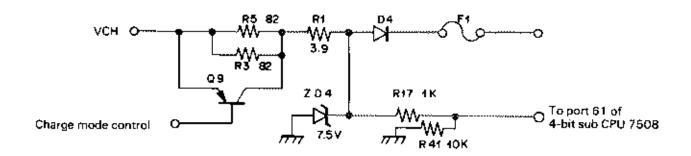

## 2.2.2.4 Charging Timing Detection

The sub-CPU program is designed to control auxiliary battery charging from the AC adaptor using the built-in clock. Connection of the AC adaptor. Port 61 of the sub-CPU goes high whenever the AC adaptor is connected and the main battery is being charged. Since port 61 is connected to the anode of the diode D4 in the charging circuit through the resistor R17, the presence of the VCH voltage can be detected.

# 2.2.2.5 Protection Against Charging Voltage Supply Failure

An overvoltage detection circuit and a reverse-current blocking circuit are provided in order to protect the batteries and their charging circuits when any abnormal voltage occurs on the output of the ac adaptor; i.e., the charging voltage. The operations of the circuits are described in the following:

# (1) Protection against low voltage

The diode inserted in the charging circuit in series prevents reverse current if the charging voltage falls below the battery voltage.

#### (2) Protection against overvoltage

If the voltage at the cathode of the zener diode (VCH) rises to +7.5V or above, the zener diode breaks down, and protect the overvoltage condition for VB+ line.

Fig. 2-10 Battery Protection Circuit

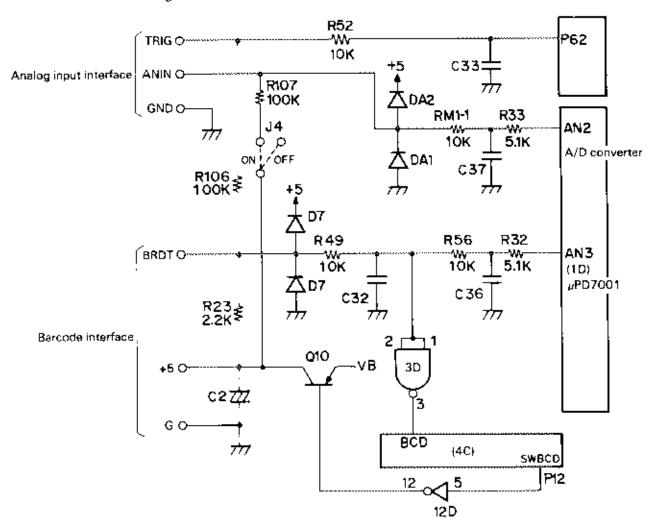

## 2.2.3 Low Voltage Detection

The 4-bit sub-CPU always monitors the battery voltage through an AD converter ( $\mu$ PD7001). When the battery voltage falls to +4.7V or below, the main battery is switched to the auxiliary battery.

#### 2.2.3.1 Battery Voltage Detection Circuit

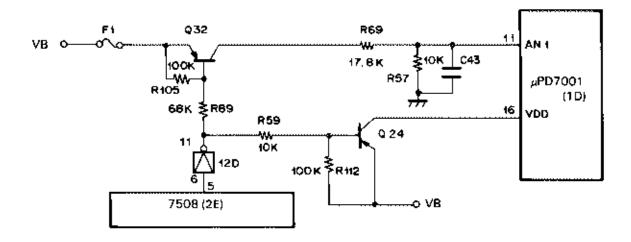

This circuit monitors the main battery voltage output through fuse F1 as follows:

• The built-in program of the 4-bit sub-CPU 7508 holds port 23 (pin 5) high. This causes IC 12D to hold its pin 11 low, putting transisters Q24 and Q32 in conduction. Q24 feeds the battery voltage (VB) to pin 16 of IC 1D (power terminal pin) to enable the AD converter μPD7001. Q32 feeds VB to the voltage divider (resistors R69 and R57). The divided voltage across R57 is fed to the AN 1 channel input of the AD converter which converts the input voltage to a 6-bit digital value representing a voltage value from 0V to 2.0V in a minimum increment of approximately 32 mV. When the digital value falls to D9H (approx. 1.7V) or below, the sub-CPU detects a low voltage condition.

Fig. 2-11 Battery Voltage Detection Circuit

The voltage supplied to the voltage divider circuit may be considered to be the same as the VB voltage. The current flowing through Q32 is so small that the voltage drop across the transistor is negligible. Thus, the divided voltage fed to the AD converter can be represented by the following expression:

$$V_{OUT} = \frac{VB(V) \cdot R57}{R69 + R57} = \frac{VB \cdot 10000}{27800}$$

The analog output (divider output) voltage equivalent to the digital value of D9H is given by multiplying the voltage represented by the least significant bit (SLB) (32 mV) by 217 (D9H). D9H is equivalent to a voltage of approximately 1.7V at the input terminal AN1, as shown below.

$$E = 2\frac{2}{256} \times 217 = 1.695 \text{ (V)}$$

where 256 voltage represented by LSB.

The VB voltage which causes the divided voltage to be detected to be a low voltage is approximately 4.7V as given by the following expression:

$$VB(x) = \frac{(R69 + R57)}{R57} \times \frac{2}{256} \times 217 \dots = 4.71 \text{ (V)}$$

Note: The above expressions do not take into account any errors such as the divider resistance errors, etc., and they actually include a total error factor of  $\pm 0.1$ V.

The above low voltage detection is performed regardless of whether power is on or off. After the after low voltage is detected, port 23 of the sub-CPU (pin 5) is back low to prevent further battery power consumption. While power is off, the voltage is **monitored every 10 seconds**.

# 2.2.3.2 Voltage Sampling During Power Off

- 12D, pin 11

1D power supply control

- 2. 1D, pin 5 SO (Serial Output)

- 3. 2E, pin 3 1D CS control

Fig. 2-12

The output at pin 11 of the IC 12D is controlled at port 23 of the 7508 (2E) sub-CPU. While power is off, it is held low for 8 ms every 10 seconds to power the IC  $\mu$ PD7001 (1D). Approximately 4 ms after the power supply to the IC, the  $\overline{\text{CS}}$  signal is input to it for channel selection. Once a channel is selected, the digital data of that channel is output to 1D, pin 5.

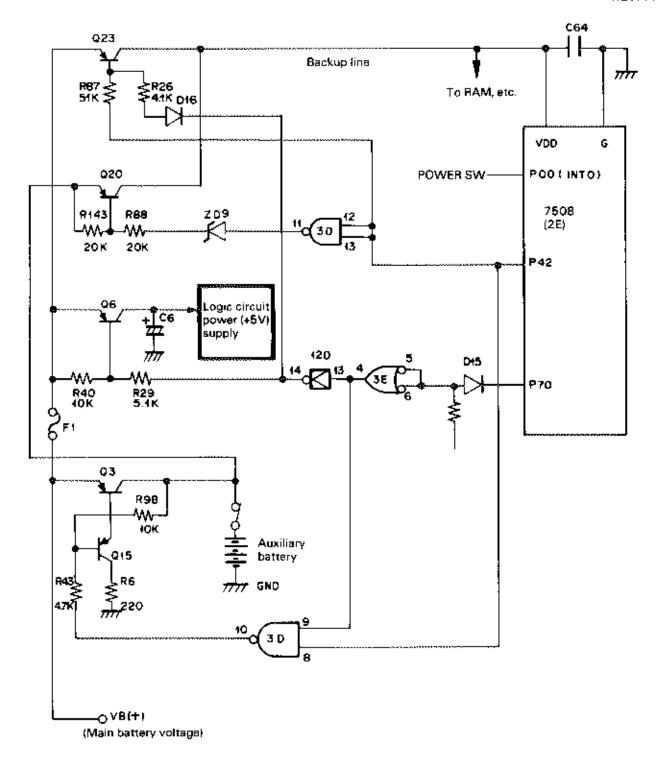

# 2.2.3.3 Circuit Operation After Low Voltage Detection

The 4-bit sub-CPU raises its port 42 (pin 37) high and controls the battery switching from main to auxiliary battery power as follows:

#### When power is on

Since port 70 (POW ON) of the sub-CPU is low when power is on, the output at pin 4 of IC 3E is inverted high, holding pin 10 of the IC 3D low as inverted by the IC. The resistor R98 (100 kohms) and the zener diode ZD8 (4V) are connected in series across this pin and the anode of the auxiliary battery.

Normally, the auxiliary battery is fully charged, since it is always charged in the trickle charge mode, and has an output voltage of 4V or above. Thus, the zener diode intermittently breaks down. This in turn causes the transistors Q15 and Q3 to alternate conduction and cut-off. This operation intermittently continues until the auxiliary battery voltage reaches 4V (discharge final voltage). When Q3 starts conduction after the discharge final voltage is reached, a current flows from the auxiliary battery, which is connected to the emitter of Q3, to the collector; i.e., to the VB line, supplementing its power which is being supplied from the main battery. This operation ensures that the computer operation, such as microcassette rewind, etc., which is in progress when low voltage is detected, is normally completed.

• The high output from port 42 of the sub-CPU is also fed to the base of transistor Q20 to enable the backup voltage supply to the VB+ line from the auxiliary battery. The backup voltage supply ensures that the computer will continue to operate until an operation termination sequence is executed and the low voltage condition is detected. Subsequently, the "CHARGE BATTERY" message is displayed on the LCD panel.

#### When power is off

• When power is off, the high level of port 70 of the sub-CPU (POW ON) holds the output at pin 4 of the IC 3E low, disabling the AND logic consisting of pins 8, 9, and 10 of the IC 3D and holding the output at pin 10 high. This disables the power supply from the auxiliary battery to the VB line. However, the power supply to the backup line through the transistor Q23 is enabled.

## 2.2.4 Backup Circuit

The following elements are backed up by the battery voltage (VB) while power is off in order to protect data in the RAMs and maintain a clock feature, etc.

**Table 2-3 Battery Protected Component**

| Location           | Element name                     | Function                                                                                                                                 |

|--------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 4D ~ 7D<br>4E ~ 7E | RAM                              | Main RAM (dynamic)                                                                                                                       |

| 9C ~ 11C           | V-RAM                            | LCO display RAM (static)                                                                                                                 |

| 2E                 | 4-bit sub-CPU                    | Power control, keyboard scanning                                                                                                         |

| 3D                 | Gate                             | Backup line control                                                                                                                      |

| 3E                 | Gate                             | Power-on signal gate                                                                                                                     |

| 4C, 6A<br>*1D      | Gate array<br>8-bit AD converter | Interrupt and clock control, etc.  Battery voltage detection and temperature change detection (for RAM refresh rate determination), etc. |

The operating voltage is supplied for 8 ms every 10 seconds.

The backup circuit is shown in Fig. 2-13. As can be seen, the circuit is normally backed up from the VB line via the transistor Q23, regardless of whether the computer is operating or not. It is backed up from the auxiliary battery when low voltage is detected.

For details of the circuit operations, refer to the descriptions on the power on/off circuit.

Fig. 2-13 Backup Circuit

# 2.2.5 DC Voltage Regulators

The MAPLE board is powered by the main or auxiliary +5V Ni-Cd battery. For circuits such as an I/O control section which requires different operating voltages and any special section which requires a larger current, however, voltage regulators are used to convert the battery voltage to the required voltages and prevent the circuit operation from being affected from a voltage drop due to use of large amount of current. The internally used voltage regulators are summarized below:

(1) +5V regulator

Purpose:

ROM capsule power source.

Control:

Enabled when the ROM capsule is reread.

Output voltage:

+5V

(2) LCD drive source regulator

Purpose:

LCD drive power source.

Control:

Always enabled.

Output voltage:

-15V (The LCD is actually driven by a voltage of 20V obtained using

the potential difference from the +5V supply.)

(3) RS-232C level source regulator

Purpose:

Sources for the RS-232C levels of  $\pm 8V$ .

Control:

Enabled only when the RS-232C or serial interface is operated.

Output voltage:

$\pm 8V$

The individual regulators are detailed in the following:

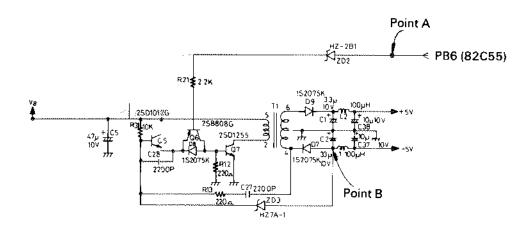

# 2.2.5.1 +5V Regulator

This regulator supplies power to the ROM capsule. When accessed, the ROM generates such a targe transient current that, if it were directly powered by the battery, a momentary low voltage condition would occur due to a voltage drop along the power line, precluding normal operation.

To prevent this, the regulator is provided as a power buffer. The circuit operation is detailed as

follows (Refer to Fig. 2-14):

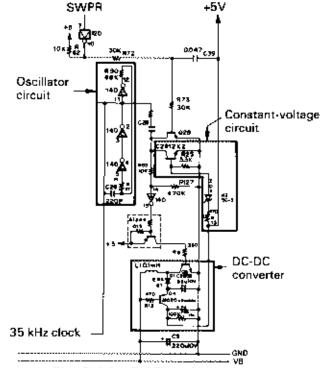

- The SWPR signal is low when power is off and is inverted high at pin 10 of the IC 12D. This signal maintains transistor Q28 in conduction, holding the collector low. Thus, the switching signal fed from pin 2 of IC 14D does not appear at the lower terminal of the capacitor C28 (collector of Q28) and the transistor Q19 is cut off, generating no output voltage.

- When power is off, transistor Q28 is cut off by the high level of the SWPR signal, and a clock signal of approximately 35 kHz is fed to pin 14 of IC 24D. This causes a pulse signal at the collector of the transistor Q19, which repeats, switching transistor Q5 on and off.

Fig. 2-14 +5V Regulator Circuit

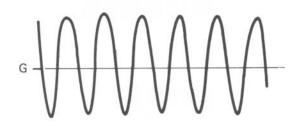

The collector of Q5 is connected to the VB line (+5V) through inductance L1 and the emitter is grounded. When the transistor repeats switching on and off, therefore, a voltage as shown in Fig. 2-15 appears at the collector. This voltage is filtered by the electrolytic capacitor, C3, through the diode D1 to a voltage that exceeds VB. This results in a potential difference across the emitter, and base of the transistor Q4, which causes the transistor to conduct, outputting a DC voltage of approximately 7V at its collector.

Because this output is connected to the constant-voltage circuit, consisting of the resistors R13 and R25, and the zener diode ZD5, the actual output voltage is fixed at +5V by the 5V breakdown voltage of the zener diode. When the Q4 output voltage rises above +5V, ZD5 breaks down at +5V, putting transistor Q22 in conduction, which forces the switching signal to ground level. The output voltage is always maintained at +5V by disabling the switching of Q5. Variation of load is handled by the relatively large capacitance of capacitor C8 (220  $\mu$ F), connected at the collector of Q4.

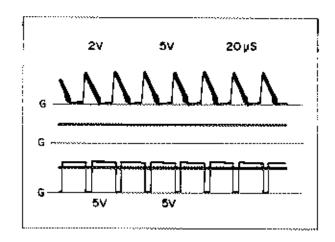

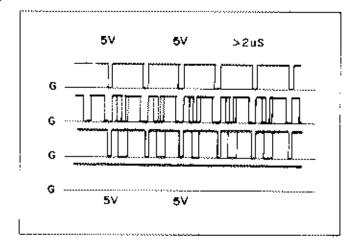

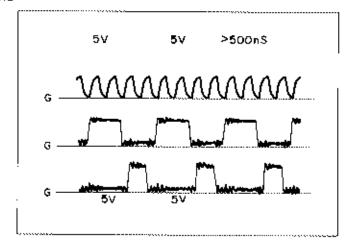

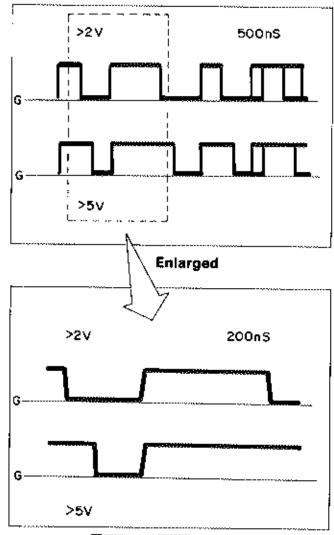

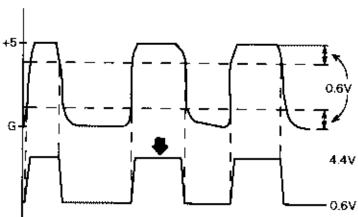

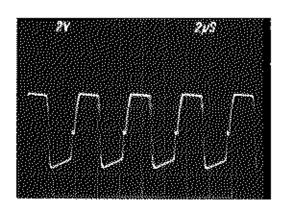

Fig. 2-15 +5V Regulator Voltages

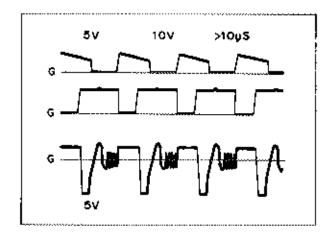

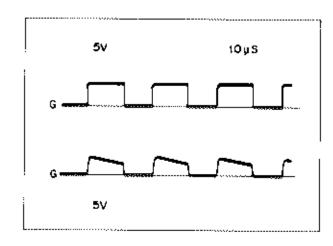

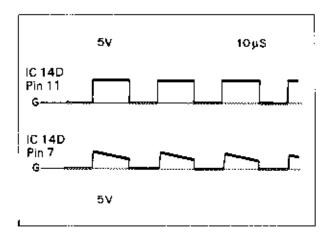

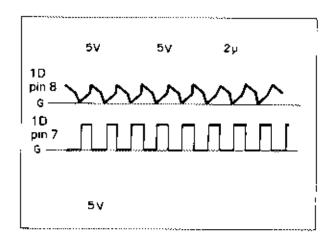

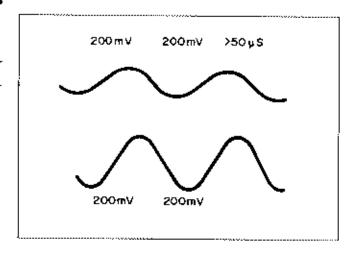

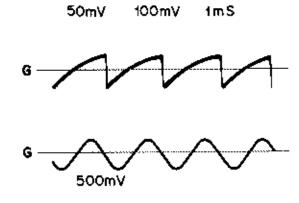

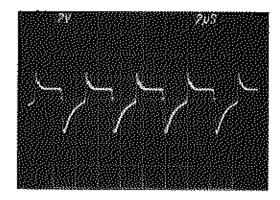

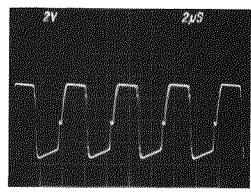

Major actual voltage waveforms are shown below.

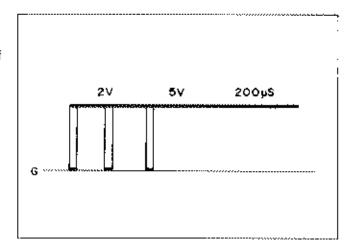

- (1) Top Test point: IC 14D, pin 14(2) Center Test point: IC 14D, pin 15

- (3) Bottom Test point: Diode D1, cathode

Fig. 2-16 Major Voltage Waveforms In +5V Regulator Circuit

Details of the above waveforms are enlarged below for clarity.

Fig. 2-17 Major Voltage Waveforms Enlarged

Though it looks as if Q5 continued to oscillate due to false images in the above photograph, it actually switches once almost every several switching clock pulses. This ratio varies depending on load.

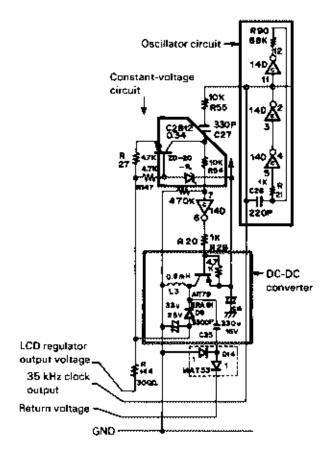

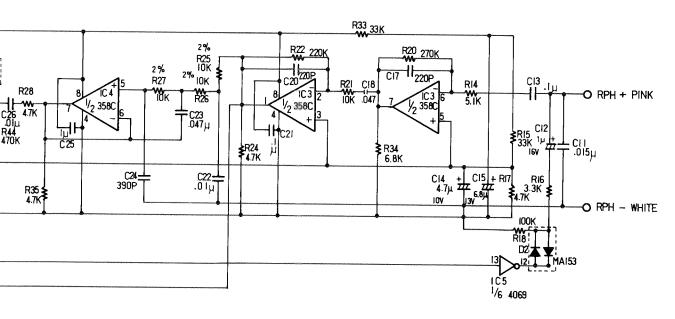

#### 2.2.5.2 LCD Drive Source Regulator

Two voltage supplies are required to drive the LCD display;

+5V is required for the logic circuit, and 20V is required for the X-Y drivers. A total potential difference of 20V is obtained by subtracting the -15V output voltage of this regulator from the +5V of the logic circuit power supply. Fig. 2-18 shows the regulator circuit.

## **Circuit Operation**

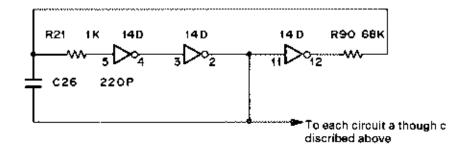

The oscillator circuit generates a clock of approximately 35 kHz when the POWER switch is turned on. This clock is fed to pin 7 of the IC 14D through R55, C27, and R54. The inverted output at pin 6 is input to the base of the transistor Q29 through R20, switching it on and off.

The emitter of Q29 is connected to the +5V logic circuit power supply and the collector is connected to ground through inductance L3. As the transistor is switched on and off by the clock signal, a voltage, as shown in Fig. 2-20, which is the counter electromotive force across L3, appears at the collector of Q29. While the collector voltage swings negative, a current flows in through diode D6, generating a negative voltage at the negative side of capacitor C17. This output is used as the LCD drive source voltage. It is also fed to the constant voltage circuit which connects the LCD drive voltage to the +5V logic circuit line through the resistor R147 and the zener diode ZD20. The zener diode has a breakdown voltage of 20V. Thus, when the output voltage rises to -15V or

Fig. 2-18 LCD Drive Source Regulator Circuit

above, the zener diode breaks down, raising the base of the transistor Q34 to the high level of +5V. This puts the transistor in conduction and its collector is driven negative, disabling the clock signal to Q29. This stops switching of Q29 and thereby lowers the output voltage. This state is maintained until the zener breakdown comes to an end. At that time, Q29 switches again. The circuit repeats this operation to produce a stable voltage of -15V.

The signal generated at the collector of Q29 is fed to the diode D14 through the capacitor C35. The negative component of the signal is removed by a current supply from ground through diode D14, while the positive voltage is fed back to the auxiliary battery through D14.

The diode, inserted across the signal line and ground, clamps the signal to the ground level, eliminating the negative component. While the positive component is fed back to the auxiliary battery via the other diode D14.

Fig. 2-19 Feedback Circuit

Fig. 2-19 is the feedback circuit redrawn for clarification. This circuit provides the charging path to the auxiliary battery while power is on.

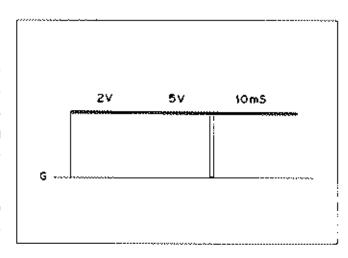

Fig. 2-20 Major Voltages of LCD Drive Power Regulator Circuit

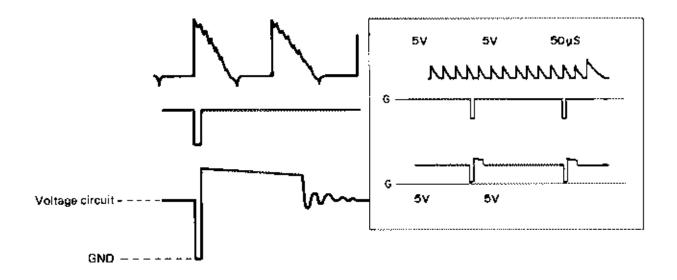

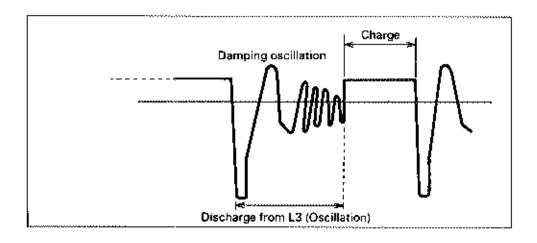

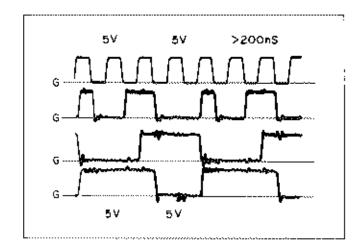

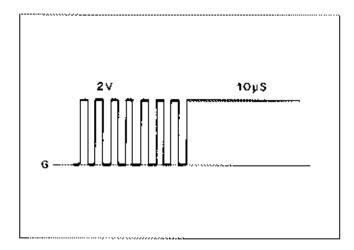

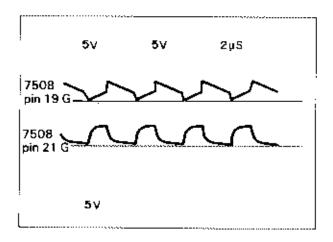

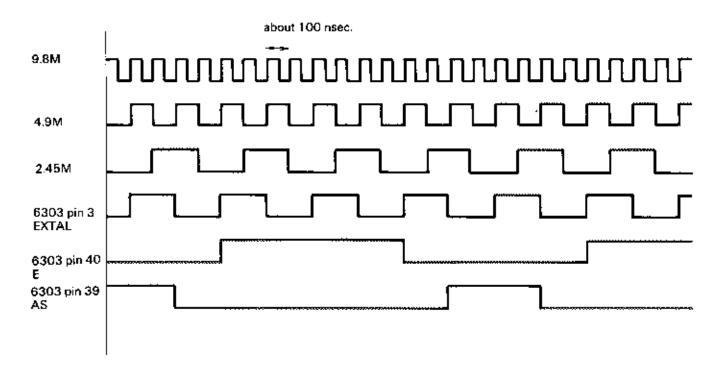

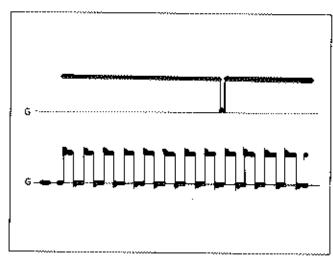

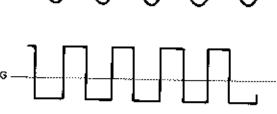

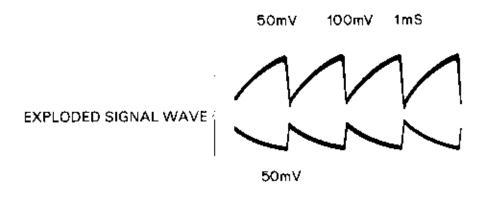

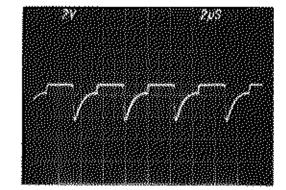

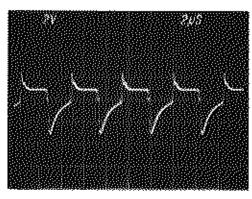

Fig. 2-21 is a photograph of the major voltage waveforms.

(Top) Measured at IC 14D, pin 7 (Center) Measured at IC 14D, pin 6 (Bottom) Measured at diode, anode

Fig. 2-21 Major Voltage Waveforms of LCD Drive Power Regulator Circuit

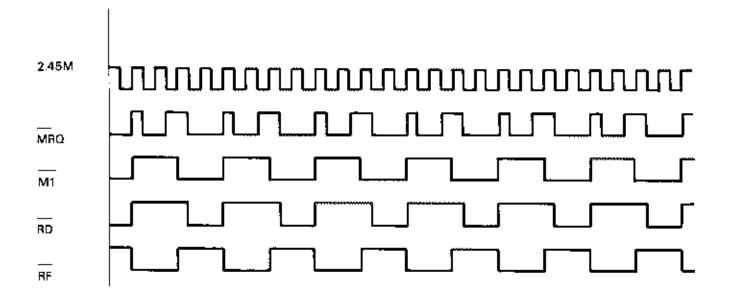

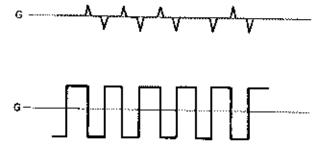

\* The detailed voltage waveform at the anode of D6, shown below, illustrates an oscillation which occurs during charge/discharge from/to the inductance L3.

Fig. 2-22 Details of L3 Discharge and Charge Cycle

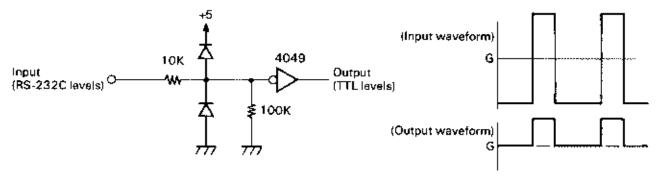

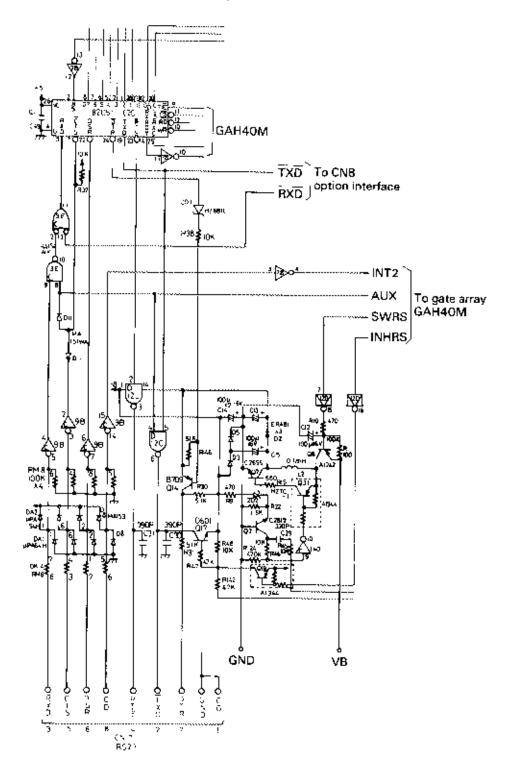

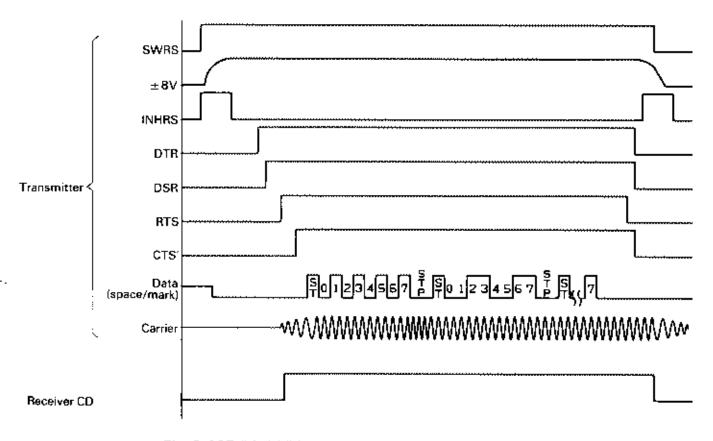

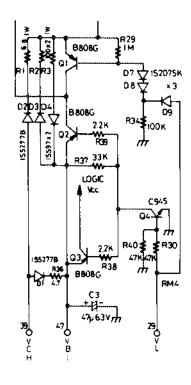

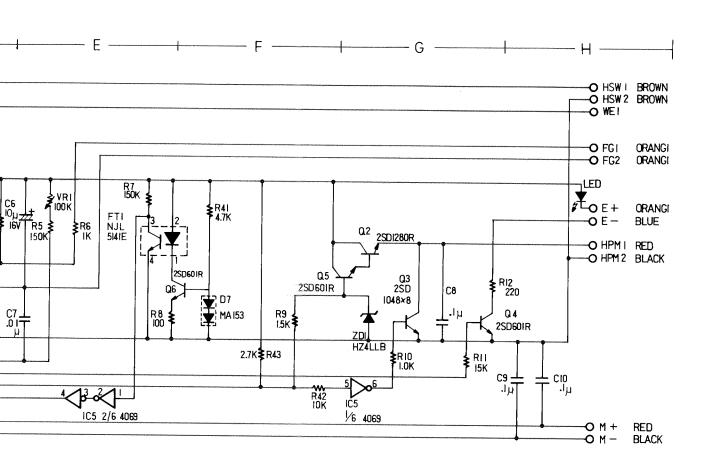

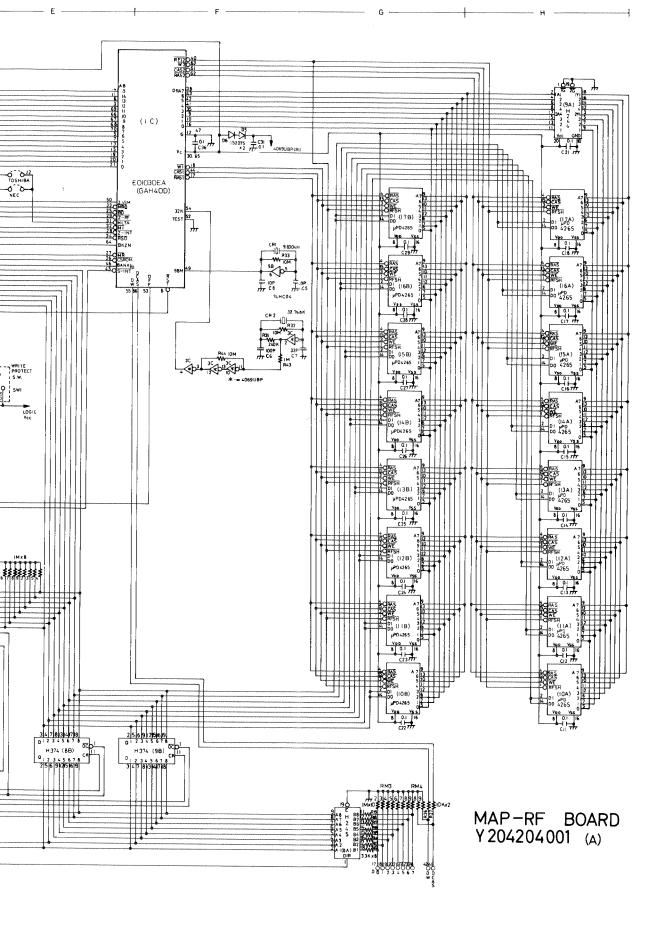

#### 2.2.5.3 RS-232C Regulator

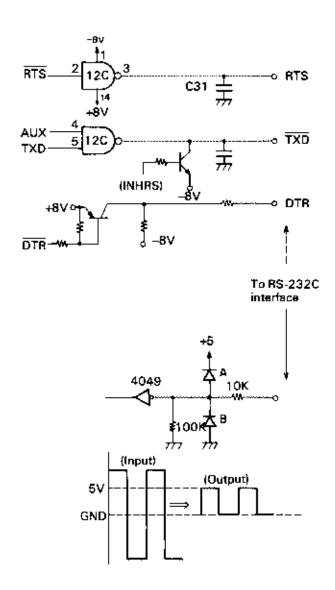

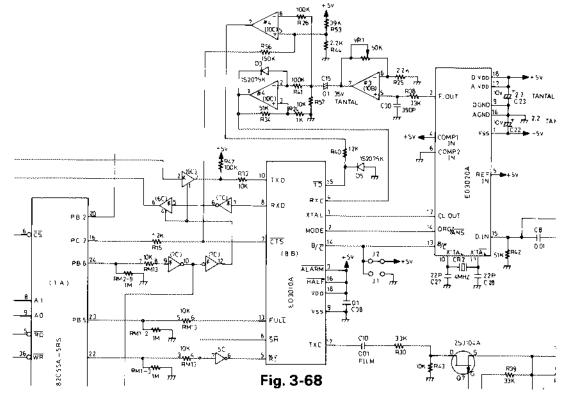

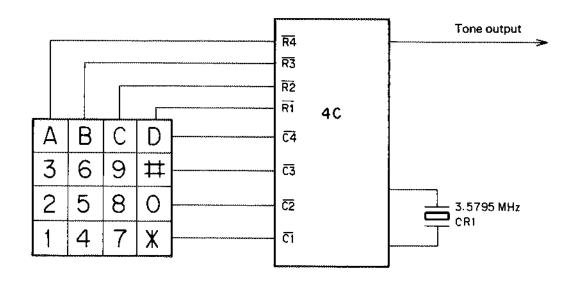

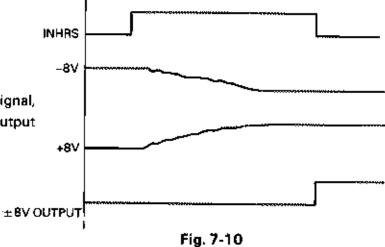

This regulator is also a DC-DC converter, which is enabled only when the RS-232C or the serial interface is used. The circuit includes a control feature which prevents its output voltage from being used for data transmission during a certain period of the rising time until the voltage is sufficiently stable to be used for the RS-232C levels. IC 4C performs this control function.

#### Circuit Operation

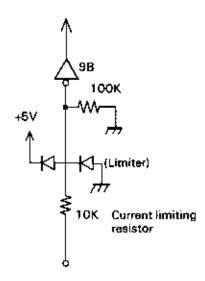

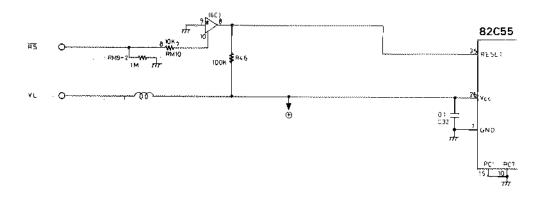

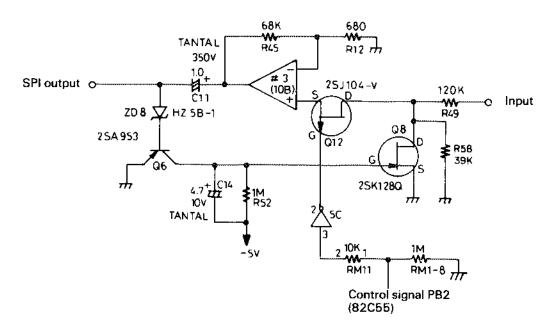

IC 4C initially outputs a high signal at pin 26 (SWRS) and a low signal at pin 27 (INHRS). The SWRS signal is inverted by IC 12D and fed to the base of the transistor Q8, turning it on. This causes the battery voltage (VB, +5V) to be output at the collector of the transistor. The INHRS signal is inverted high by 12D and then input to the base transistor Q18, cutting the transistor off. Q17 is also cut off, leaving the transmission line (TXD) floating.

A pulse signal of approximately 35 kHz, generated by a CR oscillator circuit, is supplied to pin 9 of IC 14D through R45, C29, and R46. The inverted output is fed to the base of transistor Q31, switching it on and off. This causes transistor Q17 to also start switching, thus repeating a discharge/charge from or to the inductance L2. This discharge and charge voltage is half-wave rectified by the diode D2, and the positive output voltage is filtered by capacitor C13 to produce a DC voltage of +8V. –8V is generated at the negative pole of capacitor C14 by the negative component charge to capacitor C15 and a negative voltage swing at the anode of diode D3 due to the charge.

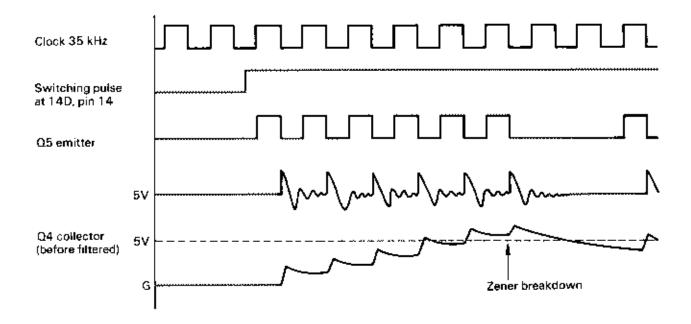

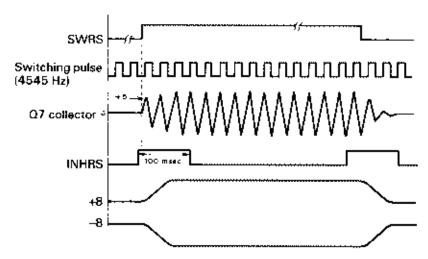

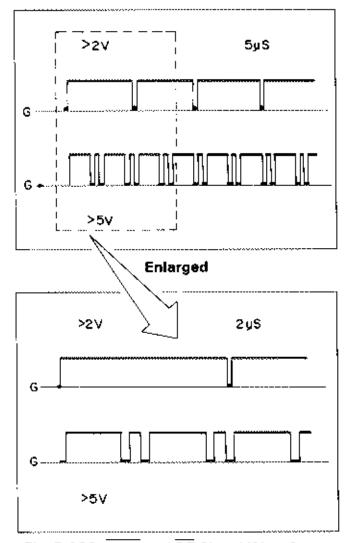

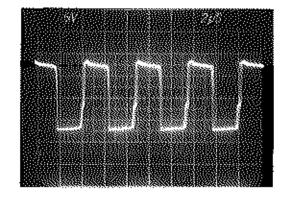

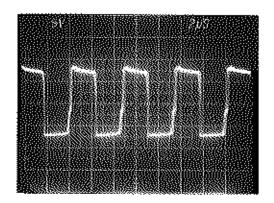

Fig. 2-23 shows the timing relationship among the voltages discussed above.

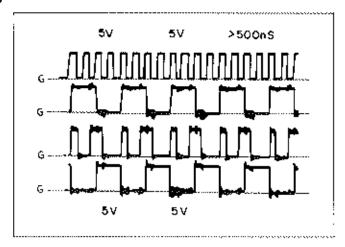

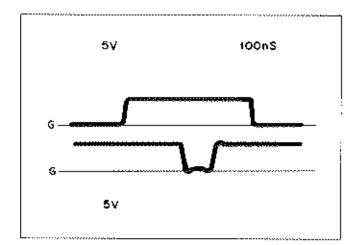

Fig. 2-23 RS-232C Power Regulator Circuit Operation Timing Diagram

The INHRS signal controls the pull-up operation (–8V) for the TXD line. It prevents irregular output voltages from reaching the TXD line. After power is turned on, if the SWRS signal has been activated, the INHRS signal is maintained low for approximately 100 ms, preventing the TXD signal line from being pulled up to unstable voltages. After power is turned off, the INHRS signal is again maintained low for approximately 100 ms in order to prevent a pull-up to unstable voltages.

## Voltage Stabilizer Circuit

The switching of transistor Q31 is controlled by a feedback from the –8V output of this DC-DC converter to the switching circuit to generate a constant output voltage.

When the -8V line voltage is lower, no potential difference is generated across the base (ground) and emitter of the transistor Q21; it is maintained in the off state because the zener diode ZD2 does not break down, and the switching circuit is not affected. When voltage rises to 7V or above, however, ZD2 breaks down at its zener voltage, generating a potential difference across the base and elimitter of Q21, turning it on. In this state, the collector is held at a negative level regardless of the switching pulse. Transistor Q31 is cut off and stops switching, lowering the output potential. This causes the breakdown of ZD2 and allows the switching to be resumed. The sequence of these circuit operations is repeated to provide two stable voltage levels of  $\pm 8V$ .

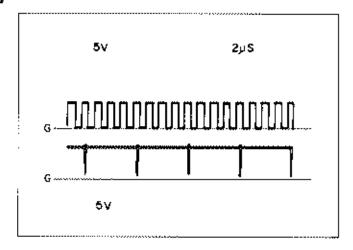

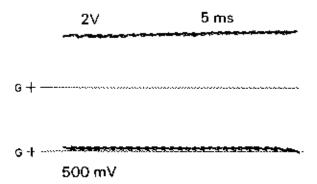

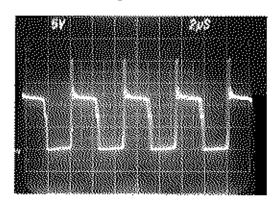

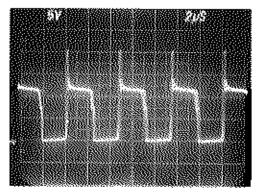

The RS-232C power regulator switching signal is shown in Fig. 2-24.

- (1) Top: Original clock signal Measured at IC 14D, pin 11.

- (2) Bottom: Input to RS Measured at IC 14D, pin 7.

Fig. 2-24

# 2.3 CPU Operations

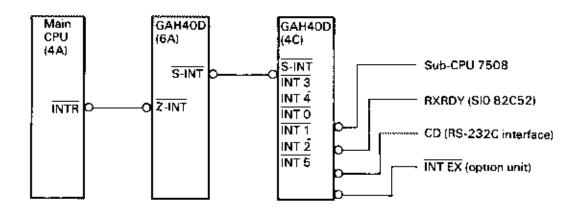

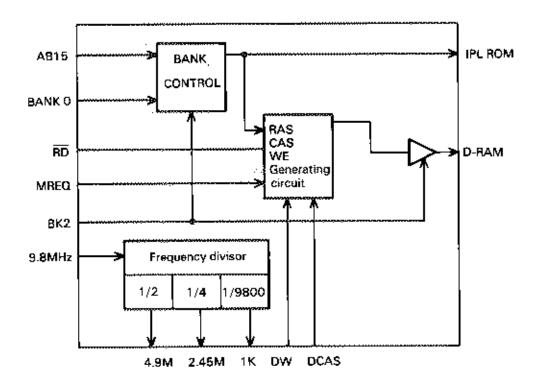

Control of memory, I/O, and various other functions is distributed among the three COMS CPUs on the MAPLE board.

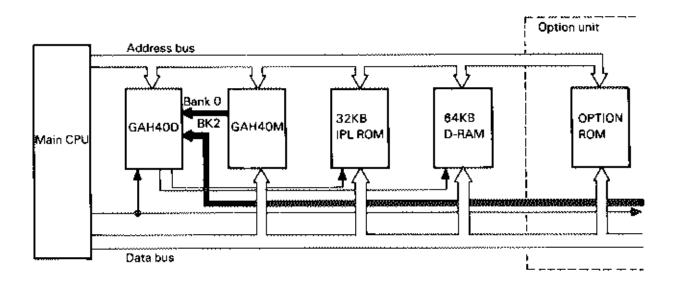

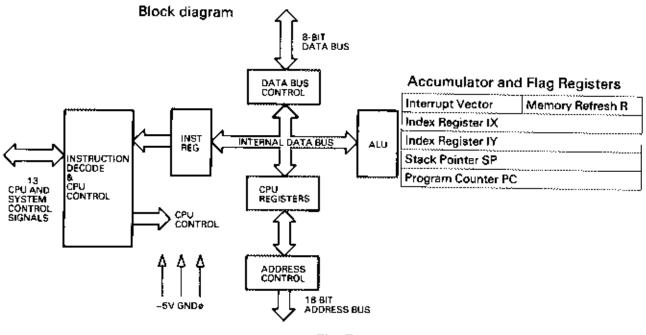

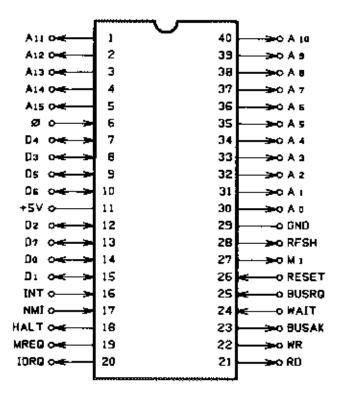

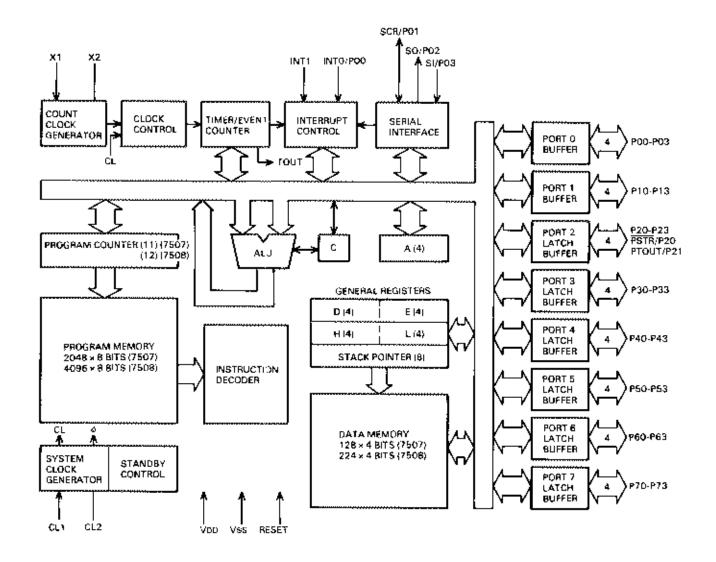

#### (1) Main CPU (Z80).....2.45 MHz

The main CPU provides overall control of circuit operations using the external 32 kB ROM (2A). Its major control functions are:

- Expand interface (CN8) control

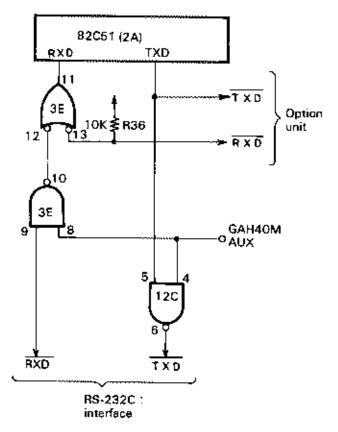

- RS-232C interface operation control via a serial controller

- 64 kB dynamic RAM read/write and refresh operation control via a gate array (GAH40D)

- RS-232C interface control via a serial controller (82C51).

- RS-232C clock supply via a baud rate generator (GAH40M).

# (2) Sub-CPU (7508).....200 kHz

The sub-CPU provides the following circuit operation control functions independent of the main CPU using the internal 4 kB masked ROM:

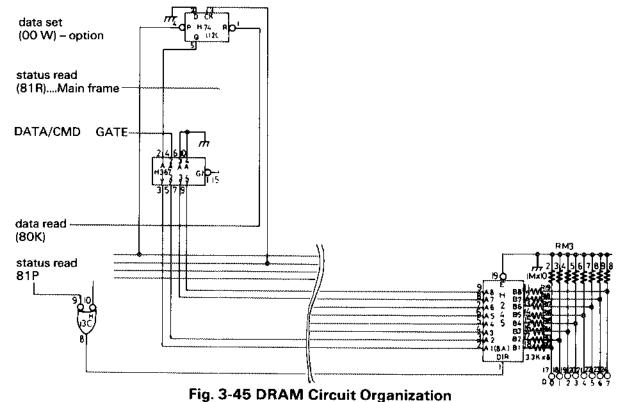

- Command exchange with the main CPU via a gate array (GAH40M)

- Power an/off control

- Change mode (normal or trickle) control

- Keyboard data entry check

- DIP switch setting read

- A-D converter enabling/disabling control

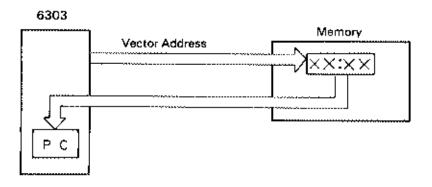

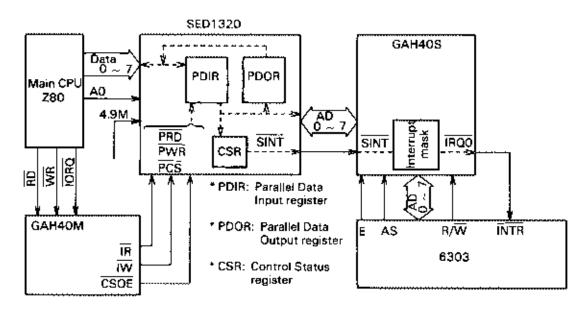

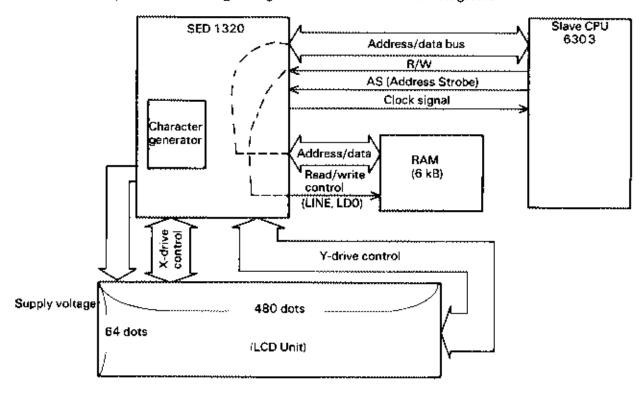

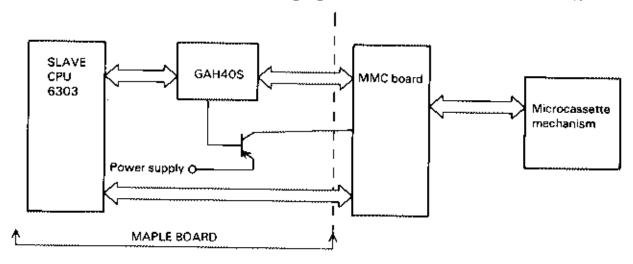

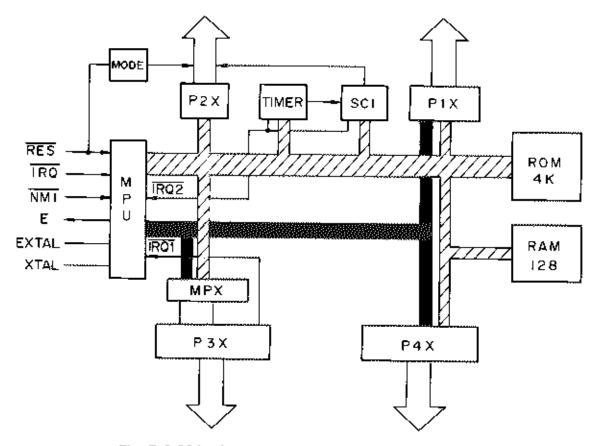

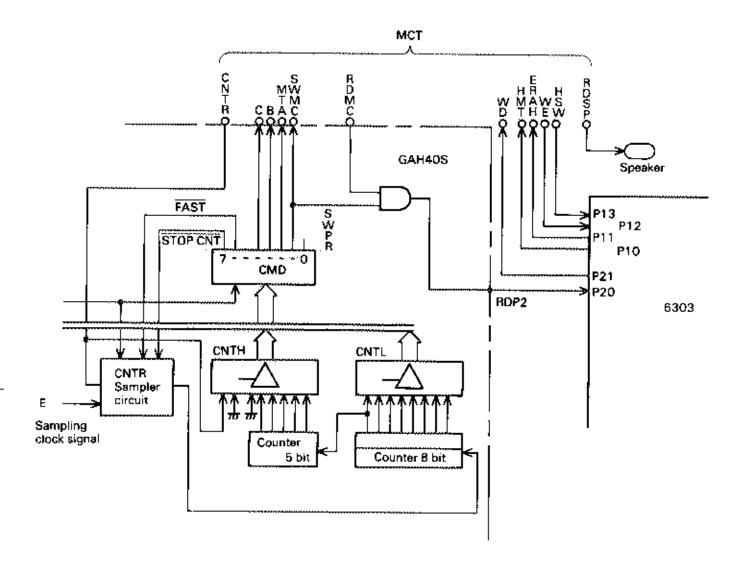

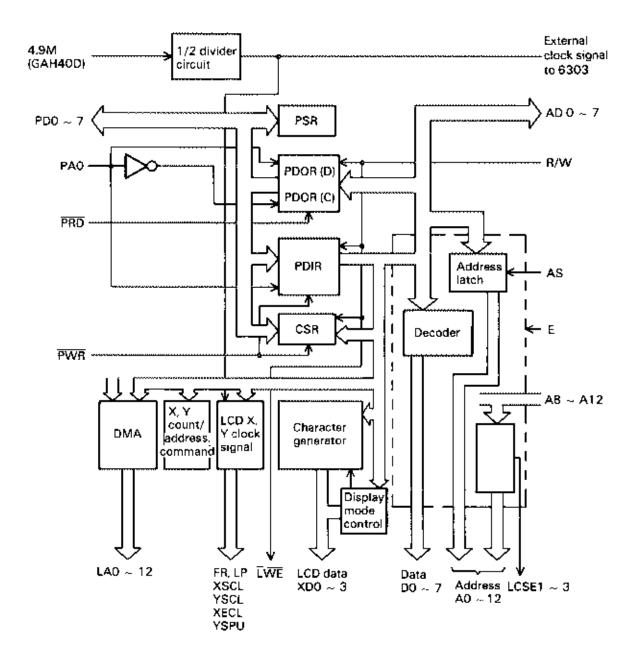

# (3) Slave CPU (6303).....614 kHz

The 6303 provides the following control functions independent of the main CPU, using the internal 4 kB masked ROM:

- Command exchange with the main CPU via the LCD controller (SED1320)

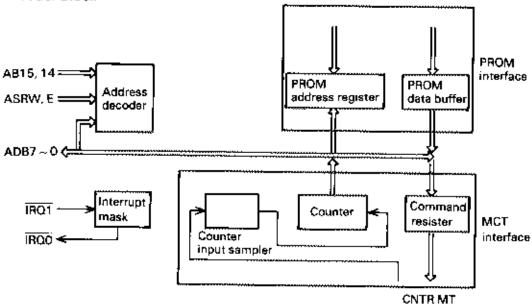

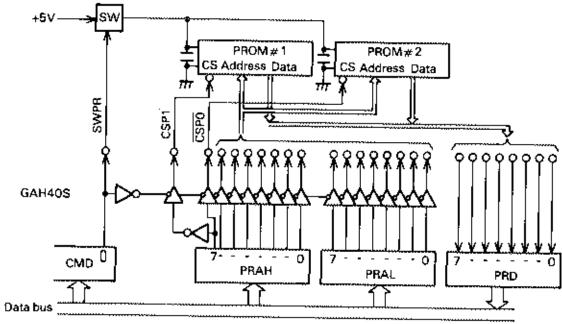

- Microcassette control via a gate array (GAH40S).

- High speed serial interface control

- Speaker output control

- LCD display control via the LCD controller (SED1320)

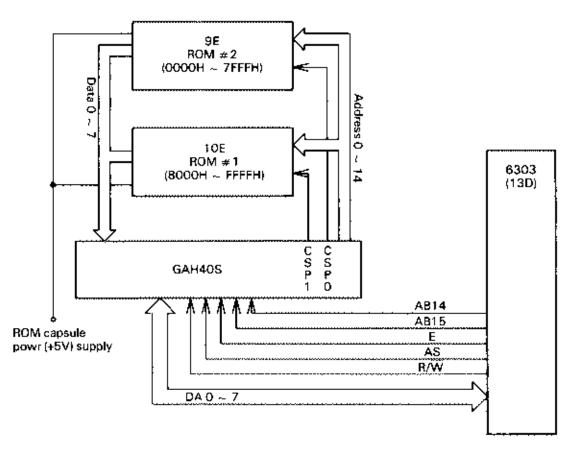

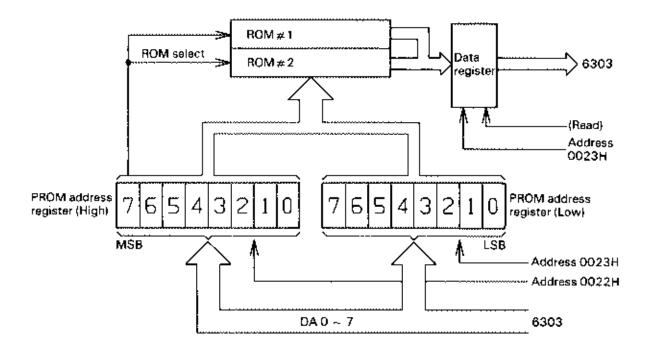

- ROM capsule read control via a gate array (GAH40S).

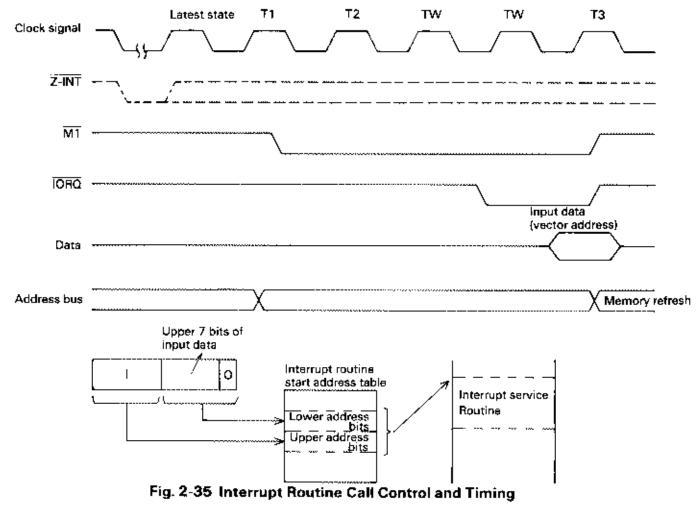

# 2.3.1 Handshaking Between Main CPU and Sub-CPUs

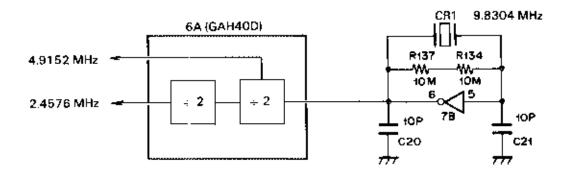

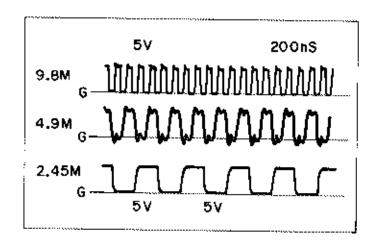

The three CPUs operate using a clock supplied from a gate array (GAH40D), which has a built-in frequency divider circuit. Data and commands are exchanged between the main CPU and the two sub-CPUs as follow:

Data exchange between Z80 and 6303: Handshaking is accomplished via the LCD controller. Data exchange between Z80 and 7508: Handshaking is accomplished via the gate array GAH40M.

Fig. 2-25 Data/Command Exchange Between Main CPU and Sub-CPUs

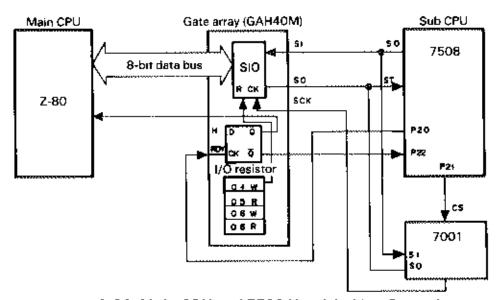

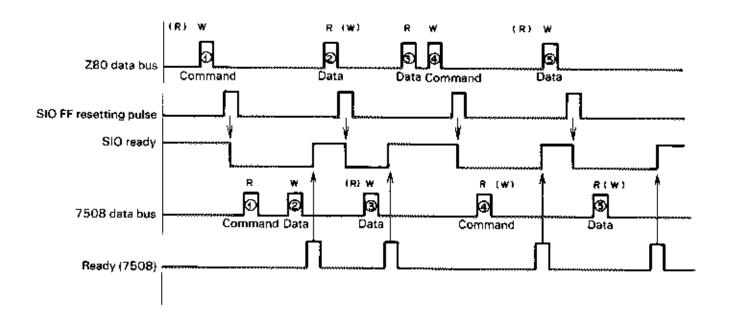

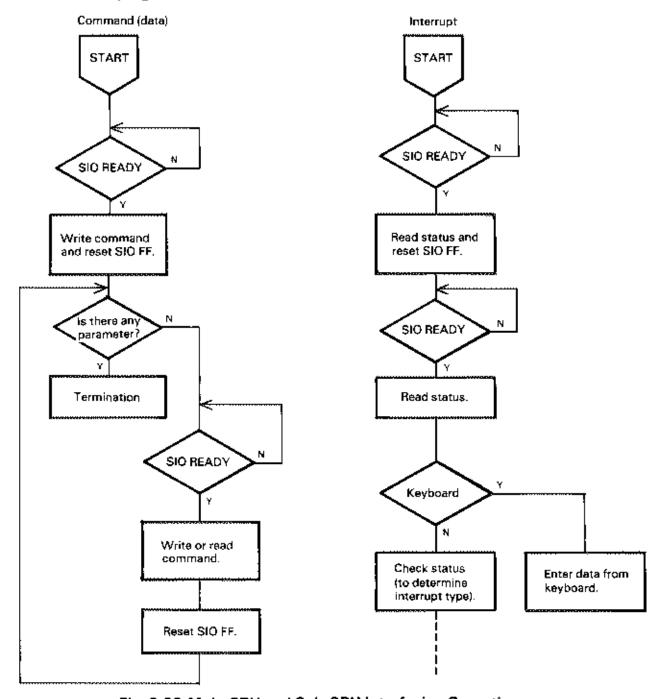

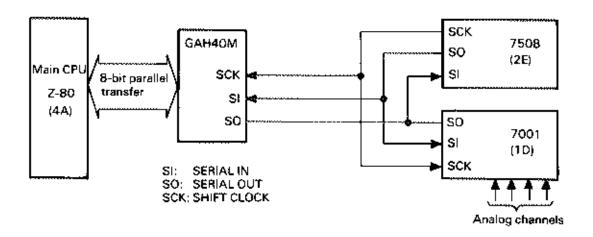

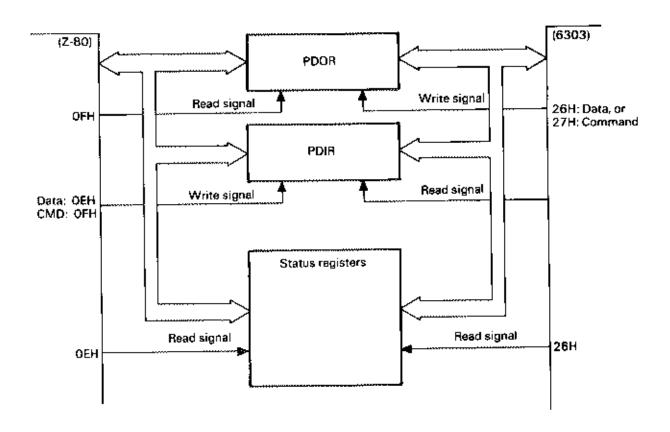

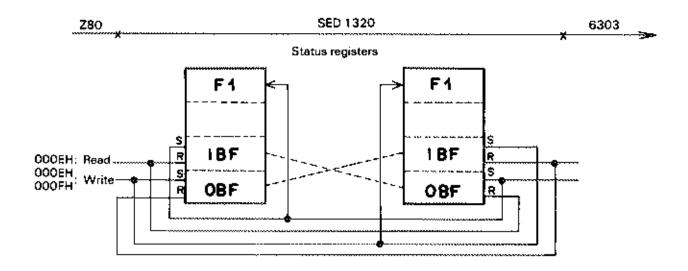

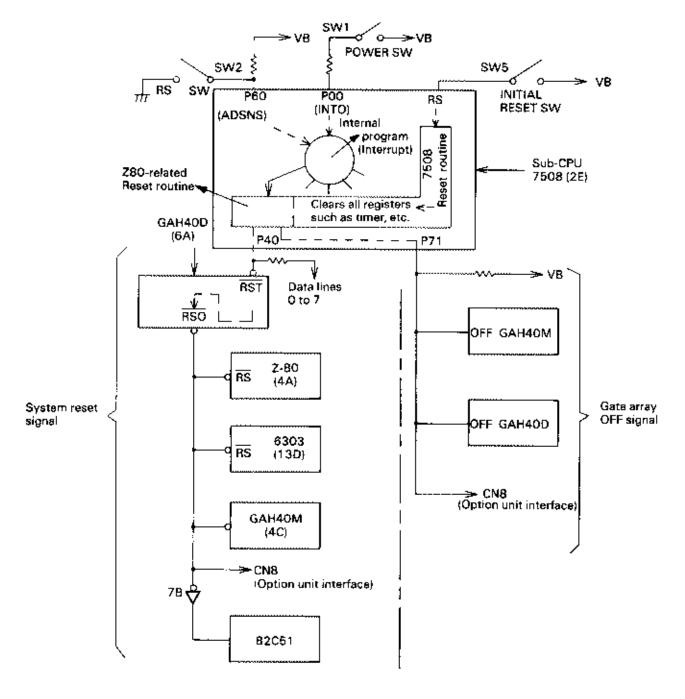

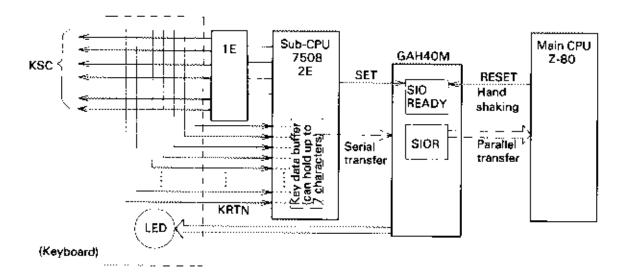

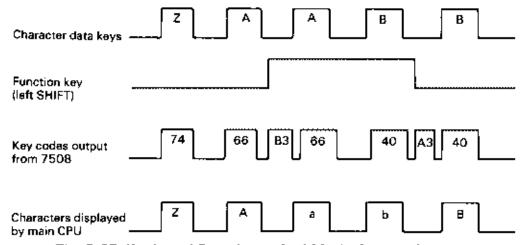

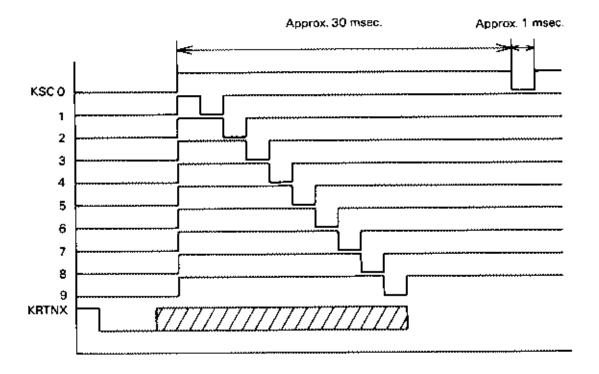

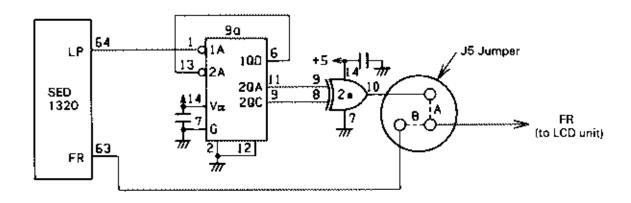

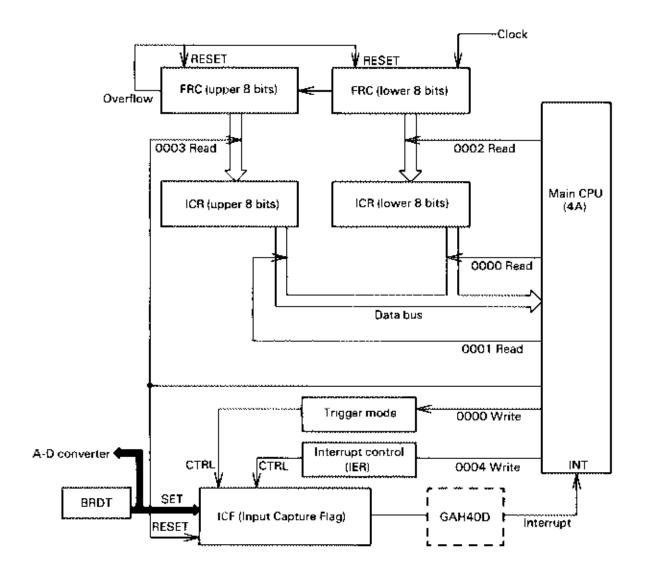

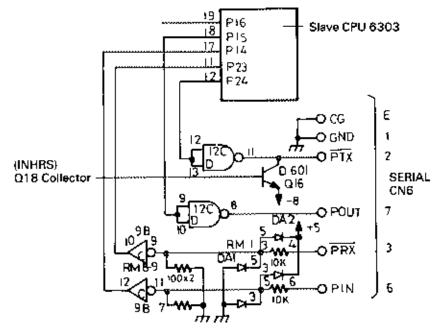

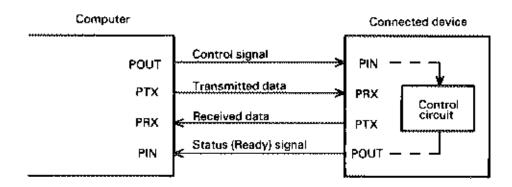

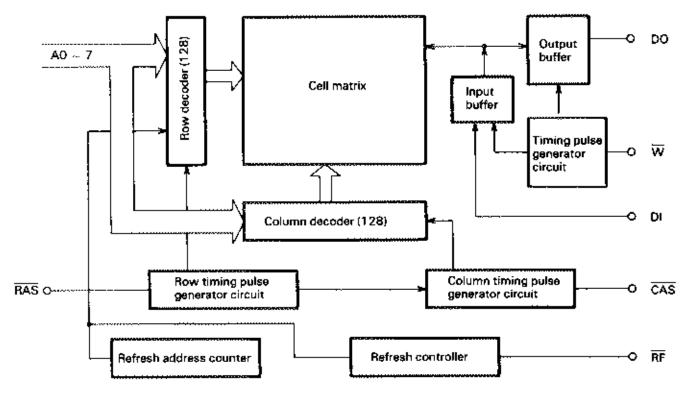

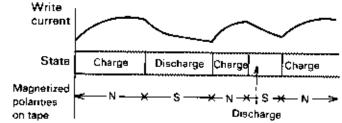

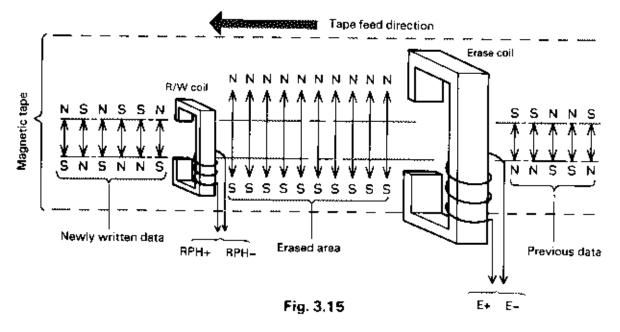

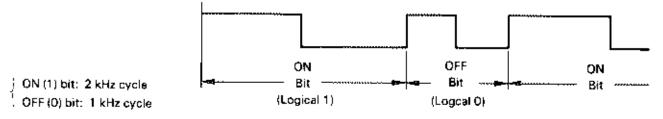

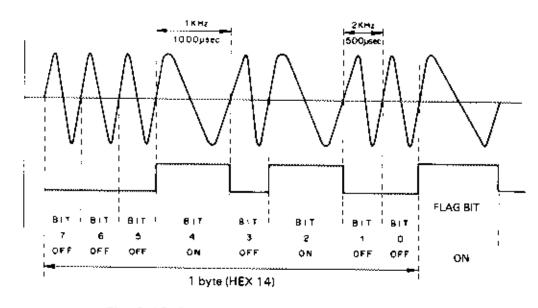

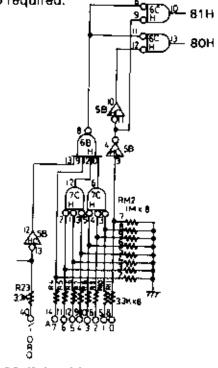

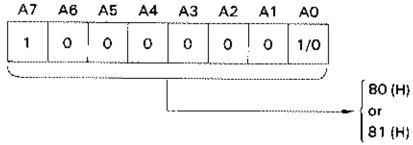

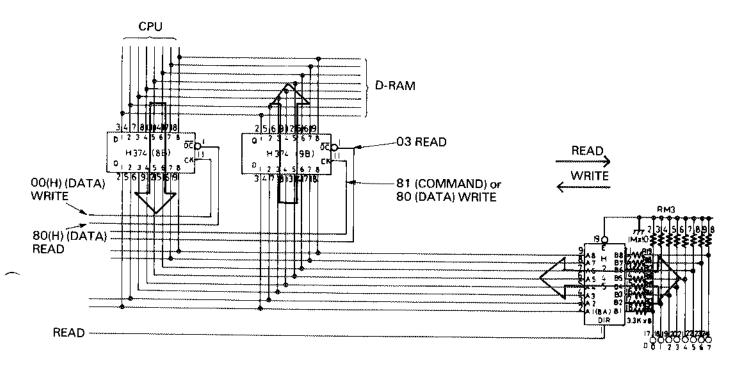

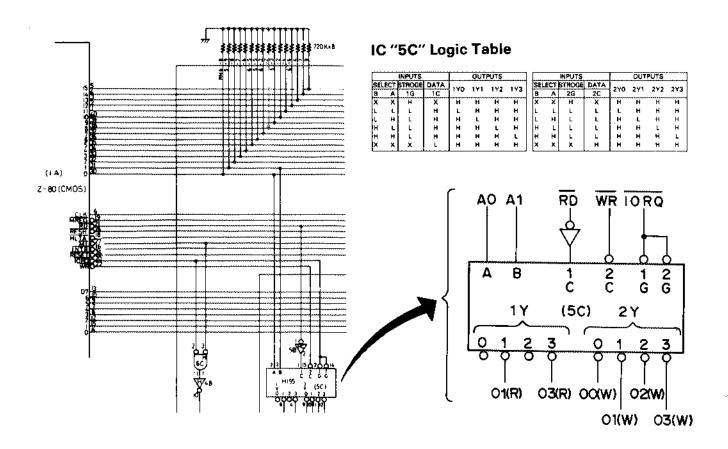

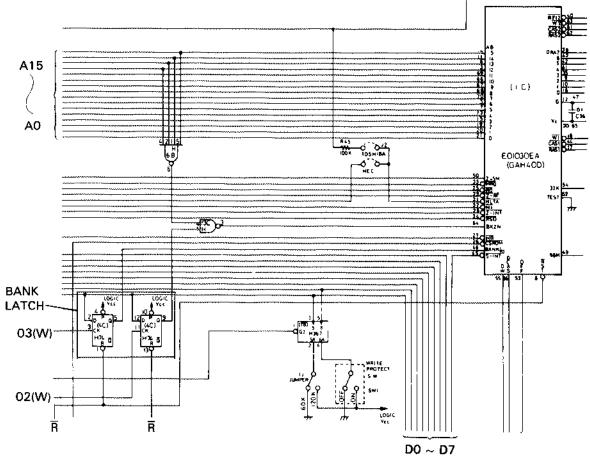

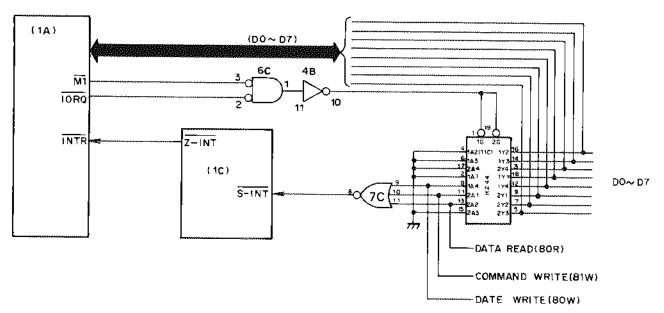

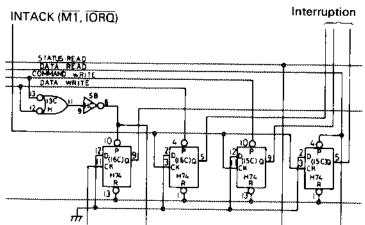

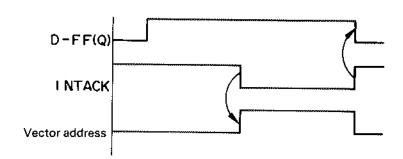

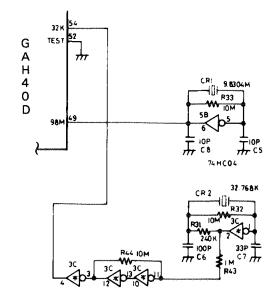

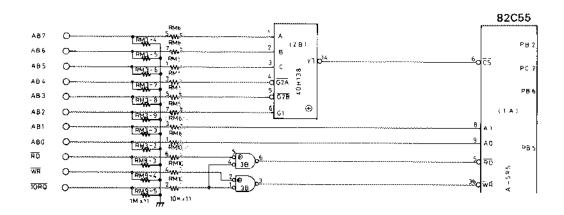

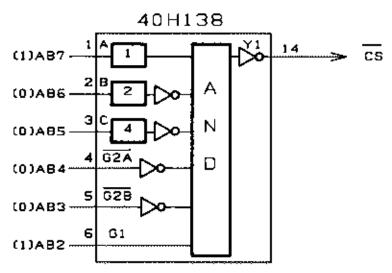

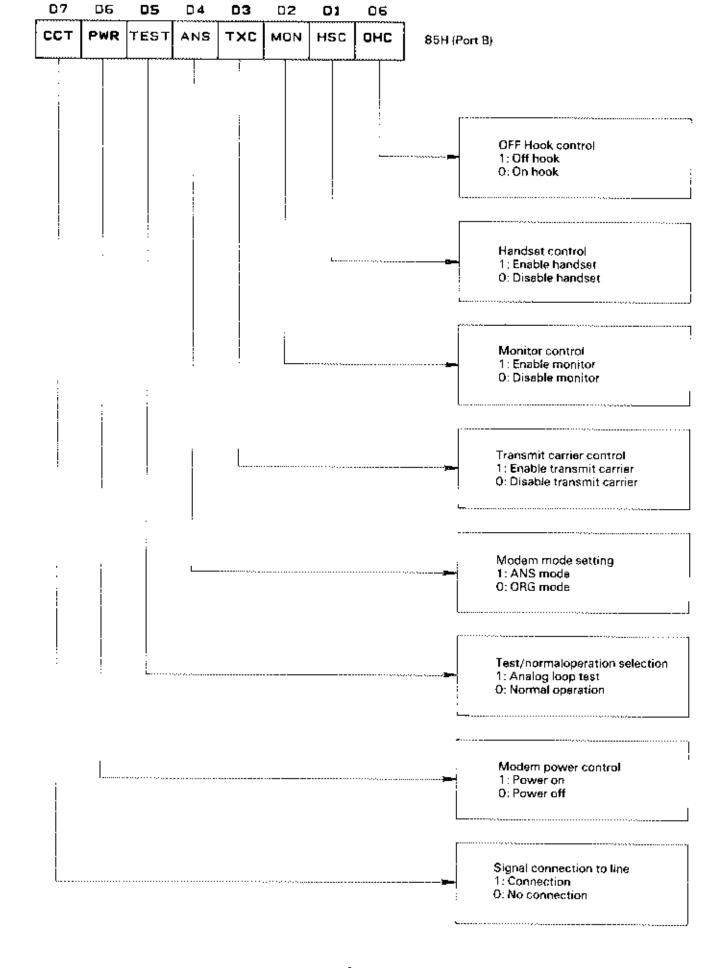

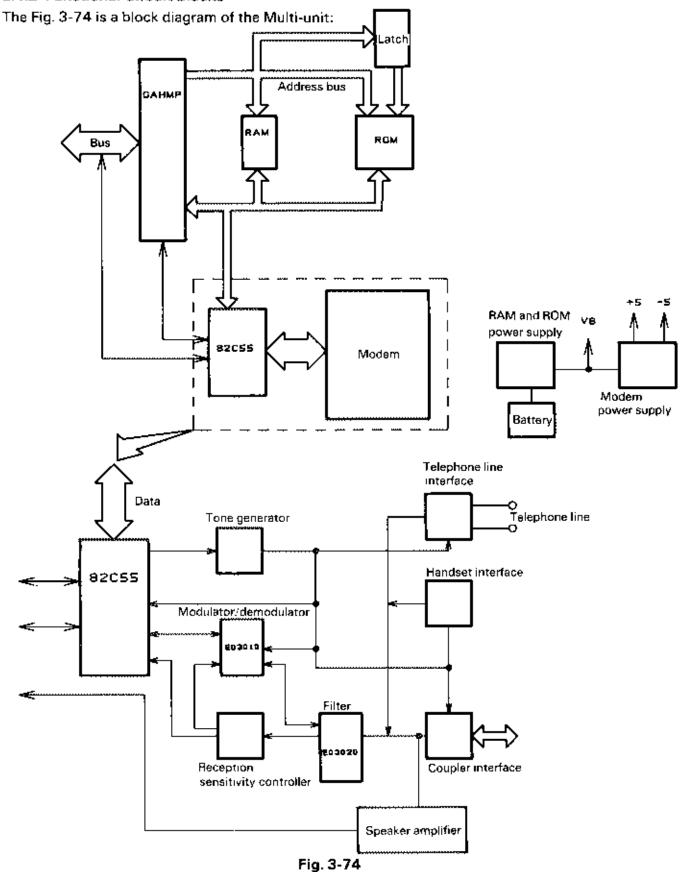

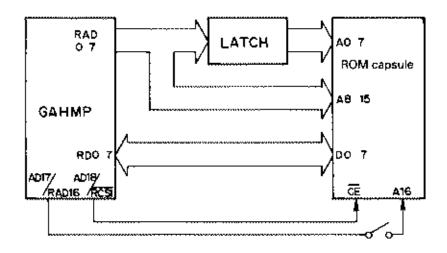

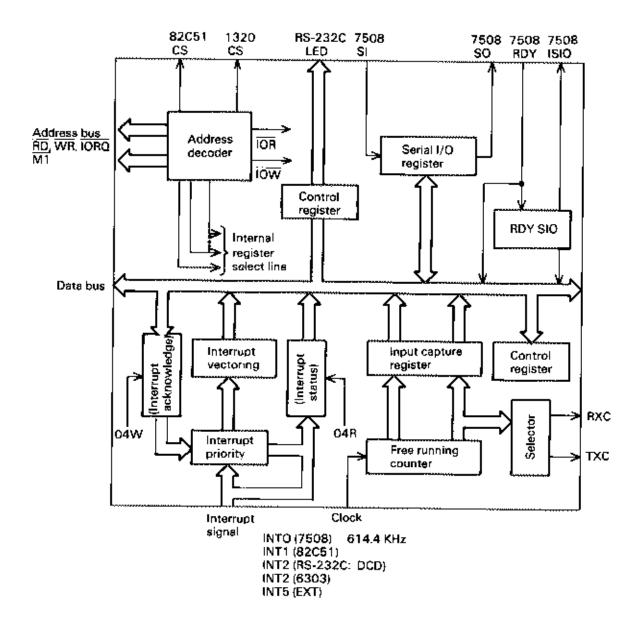

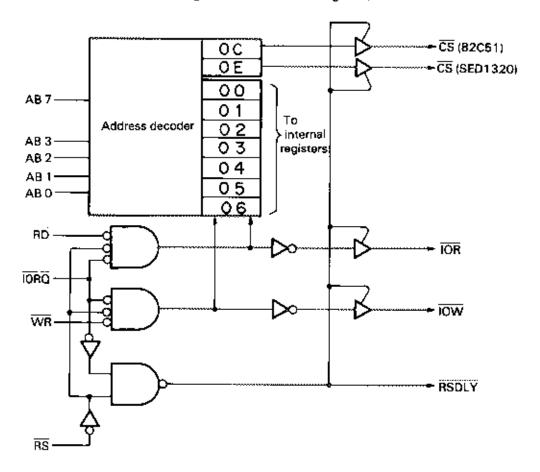

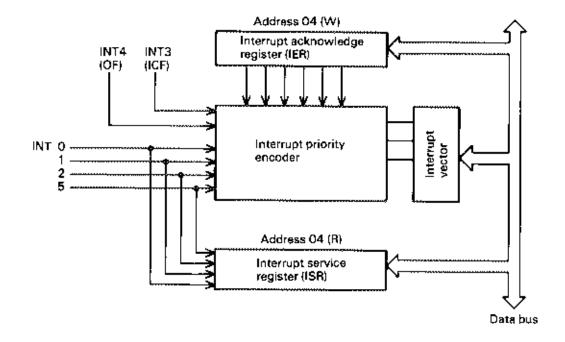

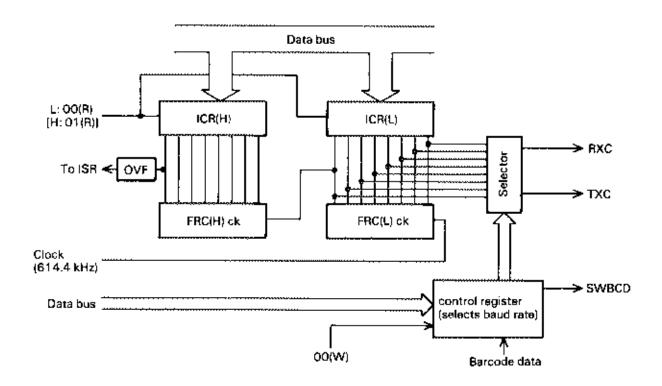

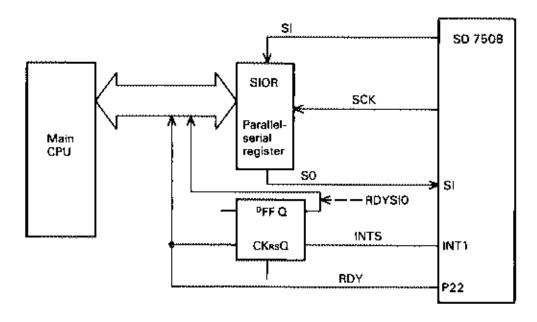

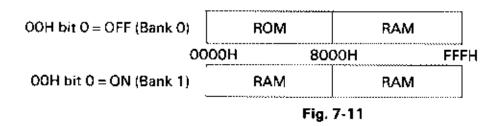

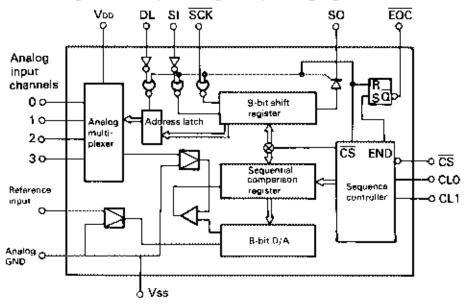

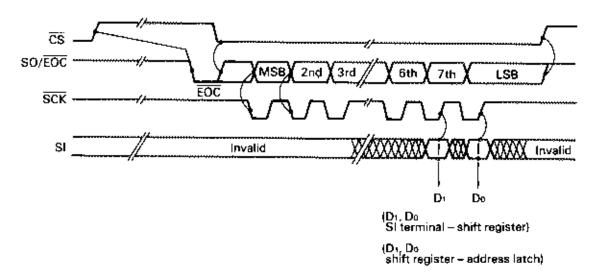

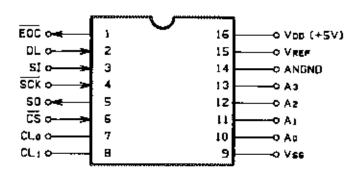

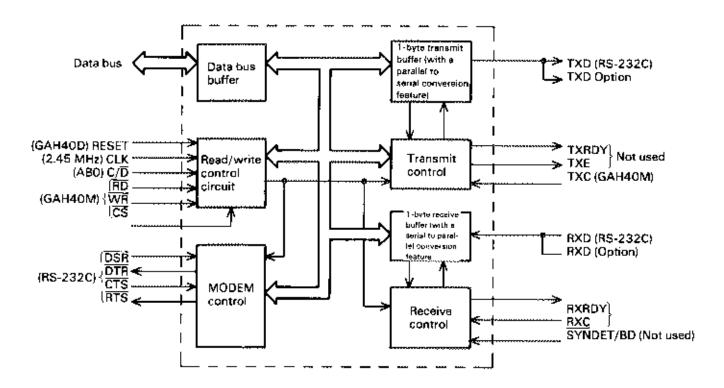

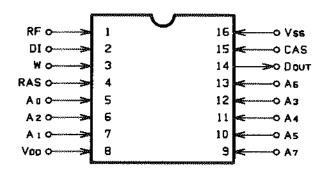

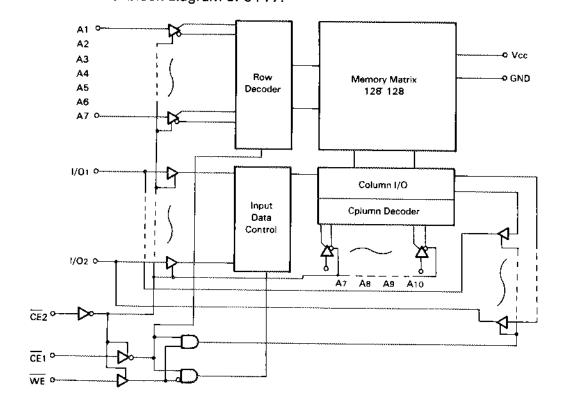

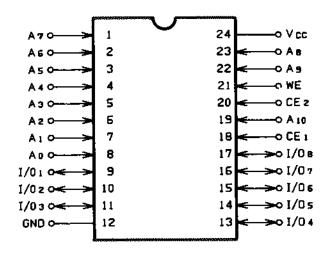

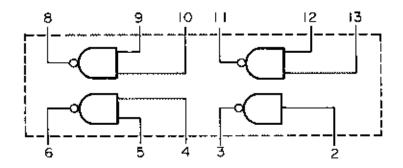

#### 2.3.1.1 Data/Command Exchange Between Main CPU and Sub-CPU 7508 via GAH40M